- 您现在的位置:买卖IC网 > PDF目录299403 > LFXP15C-4FN256C (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LFXP15C-4FN256C |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 中文描述: | FPGA, 1932 CLBS, PBGA256 |

| 封装: | 17 X 17 MM, LEAD FREE, FPBGA-256 |

| 文件页数: | 84/130页 |

| 文件大小: | 1312K |

| 代理商: | LFXP15C-4FN256C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页当前第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页

3-26

DC and Switching Characteristics

Lattice Semiconductor

LatticeXP Family Data Sheet

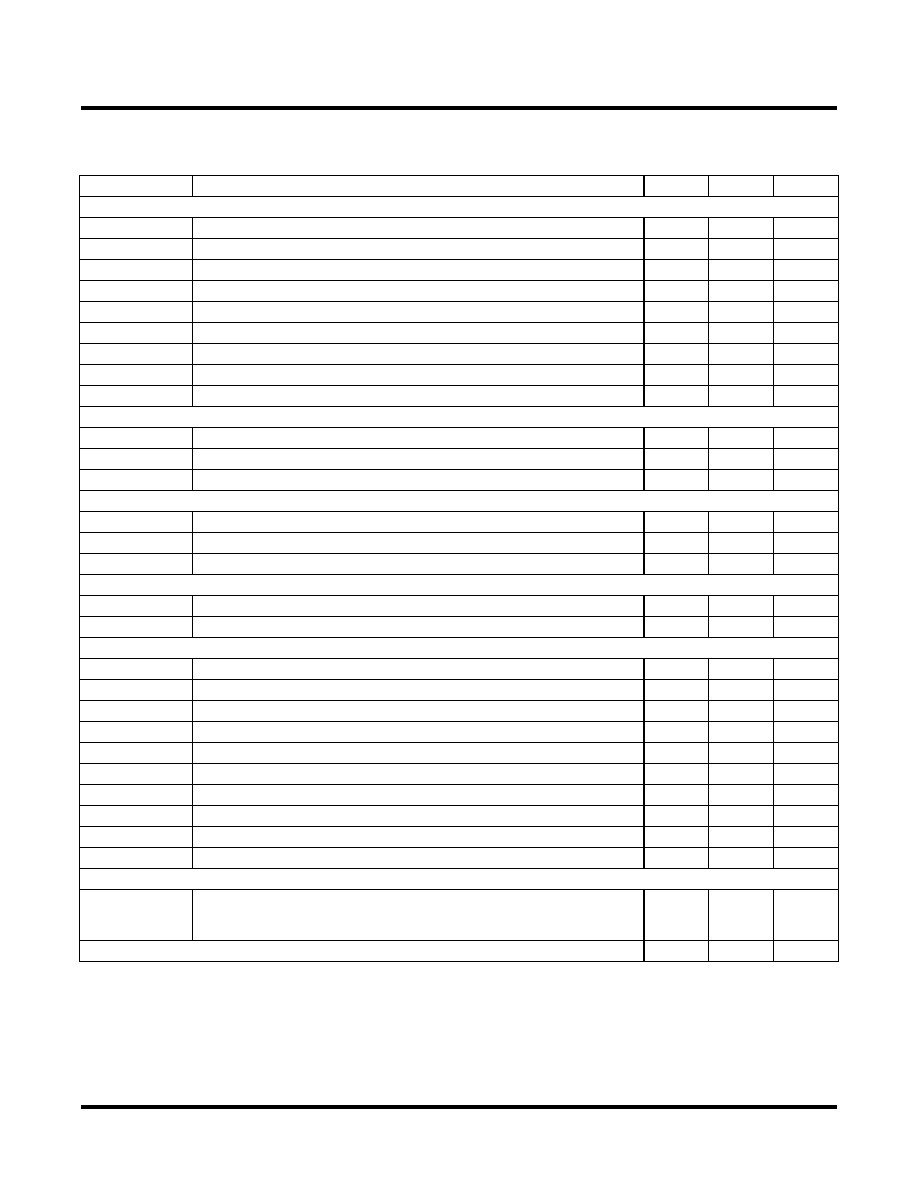

LatticeXP sysCONFIG Port Timing Specifications

Over Recommended Operating Conditions

Parameter

Description

Min.

Max.

Units

sysCONFIG Byte Data Flow

tSUCBDI

Byte D[0:7] Setup Time to CCLK

7

—

ns

tHCBDI

Byte D[0:7] Hold Time to CCLK

3

—

ns

tCODO

Clock to Dout in Flowthrough Mode

—

12

ns

tSUCS

CS[0:1] Setup Time to CCLK

7

—

ns

tHCS

CS[0:1] Hold Time to CCLK

2

—

ns

tSUWD

Write Signal Setup Time to CCLK

7

—

ns

tHWD

Write Signal Hold Time to CCLK

2

—

ns

tDCB

CCLK to BUSY Delay Time

—

12

ns

tCORD

Clock to Out for Read Data

—

12

ns

sysCONFIG Byte Slave Clocking

tBSCH

Byte Slave Clock Minimum High Pulse

6

—

ns

tBSCL

Byte Slave Clock Minimum Low Pulse

8

—

ns

tBSCYC

Byte Slave Clock Cycle Time

15

—

ns

sysCONFIG Serial (Bit) Data Flow

tSUSCDI

DI (Data In) Setup Time to CCLK

7

—

ns

tHSCDI

DI (Data In) Hold Time to CCLK

2

—

ns

tCODO

Clock to Dout in Flowthrough Mode

—

12

ns

sysCONFIG Serial Slave Clocking

tSSCH

Serial Slave Clock Minimum High Pulse

6

—

ns

tSSCL

Serial Slave Clock Minimum Low Pulse

6

—

ns

sysCONFIG POR, Initialization and Wake Up

tICFG

Minimum Vcc to INIT High

—

50

ms

tVMC

Time from tICFG to Valid Master Clock

—

2

us

tPRGMRJ

Program Pin Pulse Rejection

—

7

ns

tPRGM

2

PROGRAMN Low Time to Start Configuration

25

—

ns

tDINIT

INIT Low Time

—

1

ms

tDPPINIT

Delay Time from PROGRAMN Low to INIT Low

—

37

ns

tDINITD

Delay Time from PROGRAMN Low to DONE Low

—

37

ns

tIODISS

User I/O Disable from PROGRAMN Low

—

25

ns

tIOENSS

User I/O Enabled Time from CCLK Edge During Wake-up Sequence

—

25

ns

tMWC

Additional Wake Master Clock Signals after Done Pin High

120

—

cycles

Configuration Master Clock (CCLK)

Frequency

1

Selected

Value -

30%

Selected

Value +

30%

MHz

Duty Cycle

40

60

%

1. See Table 2-10 for available CCLK frequencies.

2. The threshold level for PROGRAMN, as well as for CFG[1] and CFG[0], is determined by VCC, such that the threshold = VCC/2.

Timing v.F0.11

相关PDF资料 |

PDF描述 |

|---|---|

| LFZ3508VXX | GENERAL PURPOSE INDUCTOR |

| LFZ2805HXX | GENERAL PURPOSE INDUCTOR |

| LF02004VTX | GENERAL PURPOSE INDUCTOR |

| LG3341-NE7501 | T-1 SINGLE COLOR LED, GREEN, 3 mm |

| LG3341-KNE9117 | T-1 SINGLE COLOR LED, GREEN, 3 mm |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LFXP15C-4FN256I | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 188 IO 1. 8/2.5/3.3V-4 Spd I RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN388C | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 268 IO 1. 8/2.5/3.3V -4 Spd RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN388I | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 268 IO 1. 8/2.5/3.3V-4 Spd I RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN484C | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 1.8/2.5/3 .3V -4 Spd RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| LFXP15C-4FN484I | 功能描述:FPGA - 现场可编程门阵列 15.4K LUTs 1.8/2.5/3 .3V-4 Spd I RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。