- 您现在的位置:买卖IC网 > PDF目录180109 > M25PE40VMW6G (STMICROELECTRONICS) 512K X 8 SPI BUS SERIAL EEPROM, PDSO8 PDF资料下载

参数资料

| 型号: | M25PE40VMW6G |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | PROM |

| 英文描述: | 512K X 8 SPI BUS SERIAL EEPROM, PDSO8 |

| 封装: | 0.208 INCH, ROHS COMPLIANT, PLASTIC, SOP-8 |

| 文件页数: | 17/62页 |

| 文件大小: | 565K |

| 代理商: | M25PE40VMW6G |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

Instructions

M25PE40

6.4

Read Status Register (RDSR)

The Read Status Register (RDSR) instruction allows the Status Register to be read. The

Status Register may be read at any time, even while a Program, Erase or Write cycle is in

progress. When one of these cycles is in progress, it is recommended to check the Write In

Progress (WIP) bit before sending a new instruction to the device. It is also possible to read

the Status Register continuously, as shown in Figure 10.

The status bits of the Status Register are as follows:

6.4.1

WIP bit

The Write In Progress (WIP) bit indicates whether the memory is busy with a Write, Program

or Erase cycle. When set to ‘1’, such a cycle is in progress, when reset to ‘0’ no such cycle is

in progress.

6.4.2

WEL bit

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch.

When set to ‘1’ the internal Write Enable Latch is set, when set to ‘0’ the internal Write

Enable Latch is reset and no Write, Program or Erase instruction is accepted.

6.4.3

BP2, BP1, BP0 bits

The Block Protect bits (BP2, BP1, BP0) are non-volatile. They define the size of the area to

be software protected against Program and Erase instructions. These bits are written with

the Write Status Register (WRSR) instruction. When one or more of the Block Protect (BP2,

BP1, BP0) bits is set to ‘1’, the relevant memory area (as defined in Table 3) becomes

protected against Page Program (PP), Page Erase (PE), Sector Erase (SE) and Subsector

Erase (SSE) instructions. The Block Protect (BP2, BP1, BP0) bits can be written provided

that the Hardware Protected mode has not been set. The Bulk Erase (BE) instruction is

executed if, and only if:

●

all Block Protect (BP2, BP1, BP0) bits are 0

●

the Lock Register protection bits are not all set (‘1’).

6.4.4

SRWD bit

The Status Register Write Disable (SRWD) bit is operated in conjunction with the Write

Protect (W) signal. When the Status Register Write Disable (SRWD) bit is set to ‘1’, and

Write Protect (W) is driven Low, the non-volatile bits of the Status Register (SRWD, BP2,

BP1, BP0) become read-only bits. In such a state, as the Write Status Register (WRSR)

instruction is no longer accepted for execution, the definition of the size of the Write

Protected area cannot be further modified.

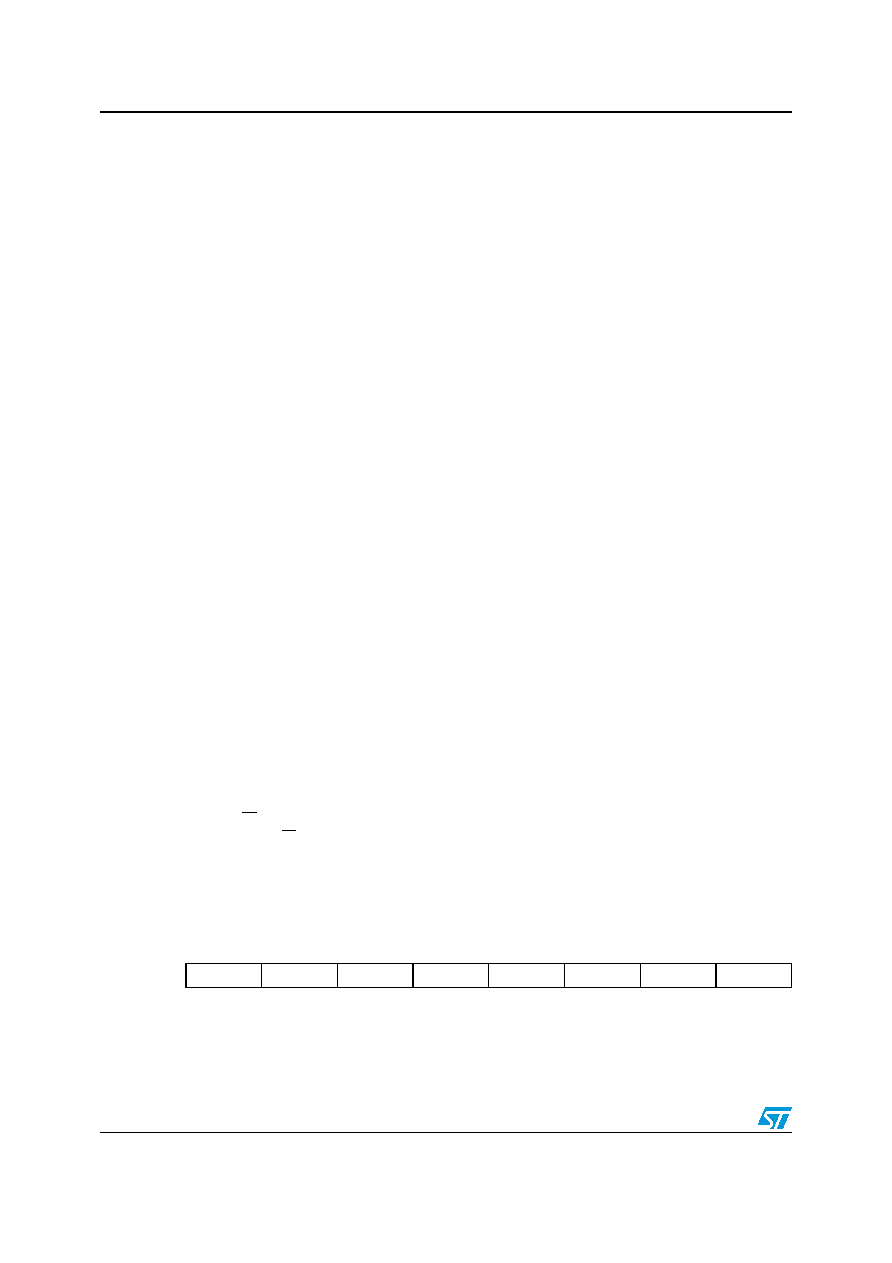

Table 7.

Status Register format(1)(2)(3)

1.

WEL (Write Enable Latch) and WIP ((Write In Program) are volatile read-only bits (WEL is set and reset by

specific instructions; WIP is automatically set and reset by the internal logic of the device).

2.

SRWD = Status Register Write Protect bit; BP0, BP1, BP2 = Block Protect bits.

3.

The BP bits and the SRWD bit exist only in the T9HX process.

b7

b0

SRWD

0

BP2

BP1

BP0

WEL

WIP

相关PDF资料 |

PDF描述 |

|---|---|

| M27C1024-10F1X | 1 Mbit 64Kb x16 UV EPROM and OTP EPROM |

| M27C1024-10F3TR | 1 Mbit 64Kb x16 UV EPROM and OTP EPROM |

| M27C1024-10F3X | 1 Mbit 64Kb x16 UV EPROM and OTP EPROM |

| M27C1024-10F6TR | 1 Mbit 64Kb x16 UV EPROM and OTP EPROM |

| M27C1024-10F6X | 1 Mbit 64Kb x16 UV EPROM and OTP EPROM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M25PE40-VMW6G | 功能描述:闪存 4 Mbit Lo Vltg Page Erasable Seral 闪存 RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel |

| M25PE40-VMW6G_NUD | 制造商:Micron Technology Inc 功能描述: |

| M25PE40VMW6P | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:4 Mbit, low voltage, Page-Erasable Serial Flash memory with byte alterability, 50 MHz SPI bus, standard pinout |

| M25PE40-VMW6P | 制造商:NUMONYX 制造商全称:Numonyx B.V 功能描述:4 Mbit, page-erasable serial Flash memory with byte alterability, 75 MHz SPI bus, standard pinout |

| M25PE40VMW6TG | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:4 Mbit, low voltage, Page-Erasable Serial Flash memory with byte alterability, 50 MHz SPI bus, standard pinout |

发布紧急采购,3分钟左右您将得到回复。