- 您现在的位置:买卖IC网 > PDF目录45186 > MB89PV950CF 8-BIT, 5 MHz, MICROCONTROLLER, CQFP64 PDF资料下载

参数资料

| 型号: | MB89PV950CF |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 5 MHz, MICROCONTROLLER, CQFP64 |

| 封装: | 0.80 MM PITCH, PIGGY BACK, MQFP-64 |

| 文件页数: | 103/110页 |

| 文件大小: | 619K |

| 代理商: | MB89PV950CF |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页当前第103页第104页第105页第106页第107页第108页第109页第110页

OPERATION

3– 6

3.3

Interrupt

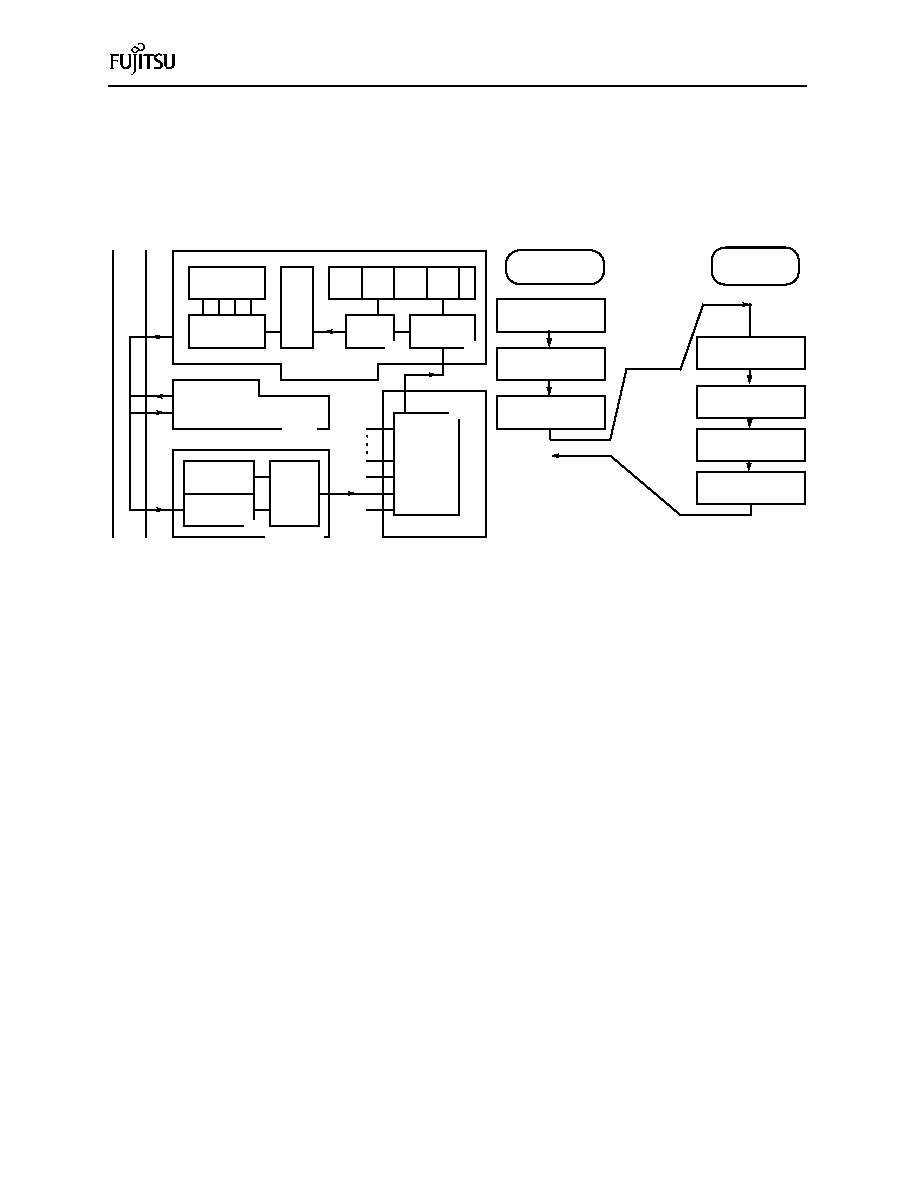

If the interrupt controller and CPU are ready to accept interrupts when an interrupt request is received from

the internal peripherals or an external-interrupt, the CPU finished the currently-executing instruction and

executes the interrupt-processing program. Fig. 3.4 shows the interrupt-processing flowchart.

Fig. 3.4 Interrupt-processing Flowchart

All interrupts are disabled right after reset. Therefore, the main program (1) should initialize interrupts .

Each peripheral generating interrupts and the interrupt-level-setting registers (ILR1 to ILR3) in the interrupt

controller corresponding to these interrupts should be initialized. The levels of all interrupts can be set by

the interrupt-level-setting registers (ILR1 to ILR3) from address 007CH to 007EH in the interrupt controller.

The interrupt level can be set from 1 to 3, where 1 indicates the highest level, and 2 the second highest

level. Level 3 indicates that no interrupt occurs. The interrupt request of this level cannot be accepted. After

setting the peripherals, the main program executes various controls (2). Interrupts are generated from the

peripherals (3). The highest-priority interrupt requests are identified from those occurring at the same time

by the interrupt controller and are transferred to the CPU. The CPU then checks the current interrupt level

and the status of the I-flag (4), and starts the interrupt processing.

The CPU performs the interrupt processing to save the contents of the current PC and PS in the stack (5)

and fetches the entry addresses of the interrupt program from the interrupt vectors. After updating the IL

value in the PS to the required one, the CPU starts executing the interrupt-processing routine.

Clear the interrupt sources (6) and process the interrupts in the user’s interrupt-processing routine. Finally,

the CPU restores the PC and PS values from the stack (8) by the RETI instruction; and then return to the

interrupted instruction.

Note: Unlike the F2MC-8 family, A and T are not saved in the stack at the interrupt time.

Internal bus

Register file

IPLA

IR

PS

I

IL

Check

Comparator

MB89600 CPU

(4)

RAM

(8)

(5)

Enable FF

Source FF

Main program

Reset clear

(1) Initialize

interrupt.

(2) Main program

execution

(8)

PC, PS restored

Restore PC, PS.

(7) Interrupt

processing

IL updated

(5)

PC, PS saved

(3)

Interrupt

generation

(4)

Level

decided

(6) Clear request.

AND

Level

comparator

Interrupt controller

(1)

(3)

(6)

Peripheral

(4)

Interrupt

processing

RETI

相关PDF资料 |

PDF描述 |

|---|---|

| MB89951PFM | 8-BIT, MROM, 5 MHz, MICROCONTROLLER, PQFP64 |

| MB89T623PFM | 8-BIT, 10 MHz, MICROCONTROLLER, PQFP64 |

| MB89623RP-SH | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PDIP64 |

| MB89625RPFV | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP64 |

| MB89W627C-SH | 8-BIT, UVPROM, 10 MHz, MICROCONTROLLER, CDIP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB89PV960 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89PV980-101 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89PV980-201 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89PW625 | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:8-bit Proprietary Microcontroller |

| MB89R112B1QN-G-AMERE1 | 制造商:FUJITSU 功能描述: |

发布紧急采购,3分钟左右您将得到回复。