- 您现在的位置:买卖IC网 > PDF目录371012 > MC144144P (MOTOROLA INC) Digital Signal Processors 44-JLCC -55 to 125 PDF资料下载

参数资料

| 型号: | MC144144P |

| 厂商: | MOTOROLA INC |

| 元件分类: | 颜色信号转换 |

| 英文描述: | Digital Signal Processors 44-JLCC -55 to 125 |

| 中文描述: | COLOR SIGNAL DECODER, PDIP18 |

| 封装: | PLASTIC, DIP-18 |

| 文件页数: | 23/44页 |

| 文件大小: | 565K |

| 代理商: | MC144144P |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

MC144144

23

MOTOROLA

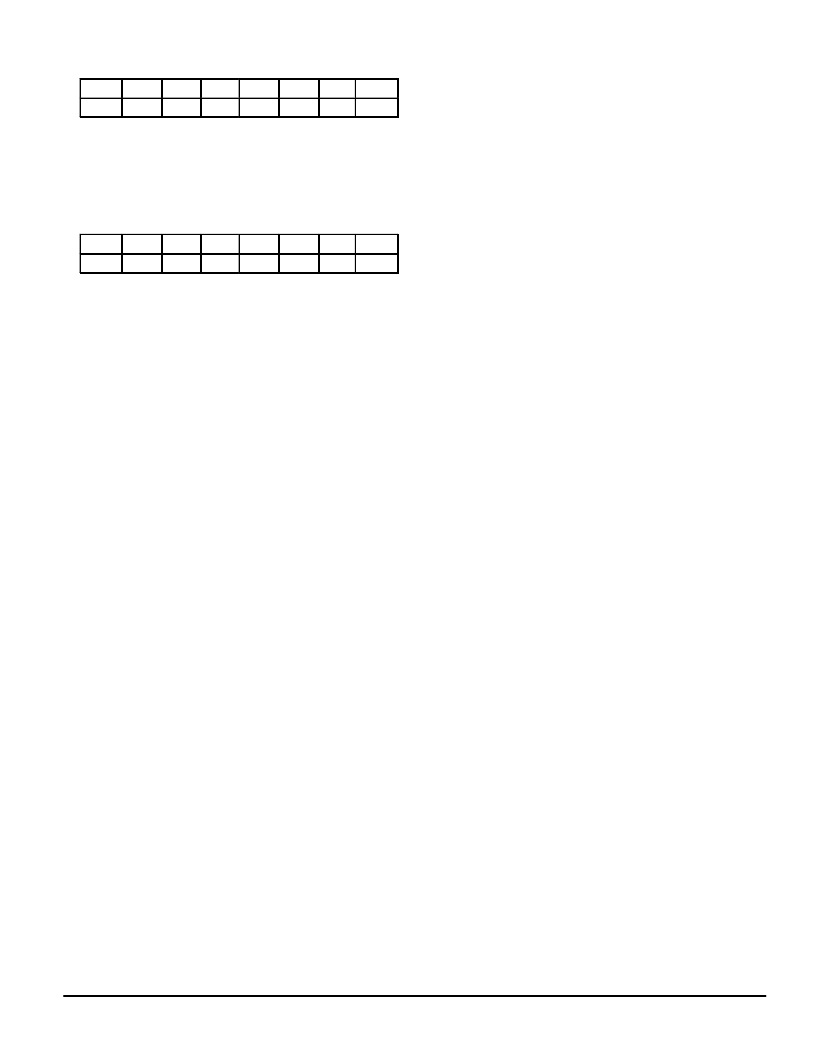

Interrupt Mask Register

—

Address = 07h

D7

D6

D5

D4

D3

D2

D1

D0

dTXT

dCAP

dXDS

dSCH

dLOK

EOF

DLE

DAV

This register identifies which activities in the interrupt re-

quest register will be used to cause an interrupt. Setting a bit

to a one enables the interrupt when the corresponding event

becomes active. Setting all bits of this register to zero dis-

ables interrupts.

Caption Activity Register — Address = 08h

D7

D6

D5

D4

D3

D2

D1

D0

T4

T3

T2

T1

CC4

CC3

CC2

CC1

Activity Bits, CC1–T4 —

Each bit will be set HIGH when a

mode setting command for its data channel has been re-

ceived. The bit will be cleared to the LOW state if no activity

is detected in that data channel during the next 12 – 16 s or if

there is a loss of lock.

XDS DATA RECOVERY

The MC144144 is able to recover extended data services

(XDS) information from the input video signal. This data, for-

matted according to the Electronics Industries Association

(EIA) recommended practice, EIA–608, can contain a wide

variety of information about current and future programs, the

channel currently tuned, other channels and miscellaneous

data including time of day.

XDS data is only present in the even field. The MC144144

can recover XDS data even while performing its normal cap-

tion decoder or OSD functions.

XDS data packets are tagged according to a class/type

system defined by EIA–608. The data may be filtered to ex-

tract only the classes of interest to the application. An addi-

tional level of filtering is provided that permits selection of

certain groups of packets that are of use in specific appli-

cations. XDS filtering reduces the traffic on the serial bus,

reduces the load of the TV/VCR control processor, and sim-

plifies external XDS decoding.

XDS data recovery is enabled by selecting one or more

classes in the XDS filter register. Optionally, a secondary fil-

ter code can be specified which further limits the packets to

be recovered. Once XDS recovery is enabled filtered data

pairs will be loaded into the serial output registers of the

MC144144 immediately upon receipt. The DAV and RD2 bits

of the serial status (SS) register will then go high, indicating

the availability of two output bytes. The external TV control

processor does not need to send a READ SELECT com-

mand in order to read these data bytes.

When the XDS filter register is set to zero (the default

state) XDS recovery is disabled.

When XDS data recovery is enabled, the external control-

ler should avoid performing any other read operation, except

SS reads, in the beginning of field 2. This is most easily ac-

complished by using the end of field (EOF) or data line end

(DLE) interrupt to locate the end of field 2 or the vertical

blanking interval (VBI) of field 1, and then perform the READ

SELECT and READ functions during this portion of the video

frame. Commands other than READ SELECTS will not inter-

fere with XDS data recovery regardless of their position in

the video frame.

Some examples of WRITE commands that could be used

to set the XDS FILTER register are shown below. The XDS

Filter register bit assignments are defined in the

Internal

Registers

section.

{C5,1F}

All XDS packets recovered.

{C5,01}

All current class packets recovered.

{C5,41}

All In band, current class packets recovered.

{C5,62}

All out of band, future class packets

recovered.

{C5,28}

Time information only recovered. Will extract

the time of day (TOD) and local time zone

(LTZ) packets from the miscellaneous class

data.

{C5,9F}

VCR Information recovered. Will select TOD,

LTZ, net ID, local call letters, impulse capture,

tape delay, composite 2, and out of band

channel number packets for recovery.

ON–SCREEN DISPLAY

OSD Operation

The user can supply information for display in an OSD

fashion through the serial port. In addition to all the normal

and extended features of the VBI data display modes, OSD

mode also has available added graphics characters, double

high and double wide characters, and the ability to position

the display anywhere on the screen with an adjustable (verti-

cal) box size. The OSD display mode can use either 13 or

15 lines per row, with box or drop shadow. The default is

15 scan lines per row and drop shadow. Enhanced attributes

are always enabled.

The 15 scan line per row display can only show 13 rows

on–screen when in the NTSC mode. Rows 14 and 15 will be

off–screen and should not be addressed. In the PAL mode all

rows will be visible.

The 15 scan lines per row mode display can show the full

graphic characters and accented capital letters and des-

cenders without the potential overlap that would result from

the 13 scan line per row display. If the OSD display mode is

changed to a 13 scan line per row mode, the top two scan

lines of any graphics or accented capital letter will be “ored”

together with the bottom two scan lines from the row above.

In 13 line – drop shadow mode this will also result in a side

shadow effect. Graphics characters should not be used in

the 13 line – drop shadow mode.

The OSD character set is shown in Figures 8 and 9. There

are 256 possible addresses and Figure 8 shows the address

map in the range 00h – BFh. This portion of the addressable

space contains the control bytes and regular character set.

Figure 9 shows the address map in the range C0h – FFh.

These addresses are shared by the extended character set

and the graphics character set. Any particular OSD screen

can use one or the other of these sets of characters but not

both.

The character set in force is controlled by the type of dis-

play mode being invoked. When drop shadow is being used,

by default, the graphics character set will be displayed in re-

sponse to an address in the C0h – FFh range. However, if a

BOX display is used, the extended character set is invoked.

相关PDF资料 |

PDF描述 |

|---|---|

| MC14415DW | Digital Signal Processors 40-CDIP SB -55 to 125 |

| MC14415FL | Quad Precision Timer/Driver |

| MC14415FP | Quad Precision Timer/Driver |

| MC14415VL | Digital Signal Processors 68-CPGA -55 to 125 |

| MC14415VP | Digital Signal Processors 68-LCCC -55 to 125 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC14415FP | 制造商:Motorola Inc 功能描述: |

| MC14416P | 制造商:Motorola Inc 功能描述: 制造商:Motorola Inc 功能描述:TIME-SLOT ASSIGNER, 22 Pin, Plastic, DIP |

| MC14419P | 制造商:Motorola Inc 功能描述:ENCODER, 16 Pin, Plastic, DIP |

| MC14433P | 制造商:Motorola Inc 功能描述: |

| MC1443G | 制造商:Motorola Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。