- 您现在的位置:买卖IC网 > PDF目录371012 > MC144144P (MOTOROLA INC) Digital Signal Processors 44-JLCC -55 to 125 PDF资料下载

参数资料

| 型号: | MC144144P |

| 厂商: | MOTOROLA INC |

| 元件分类: | 颜色信号转换 |

| 英文描述: | Digital Signal Processors 44-JLCC -55 to 125 |

| 中文描述: | COLOR SIGNAL DECODER, PDIP18 |

| 封装: | PLASTIC, DIP-18 |

| 文件页数: | 4/44页 |

| 文件大小: | 565K |

| 代理商: | MC144144P |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

MC144144

4

MOTOROLA

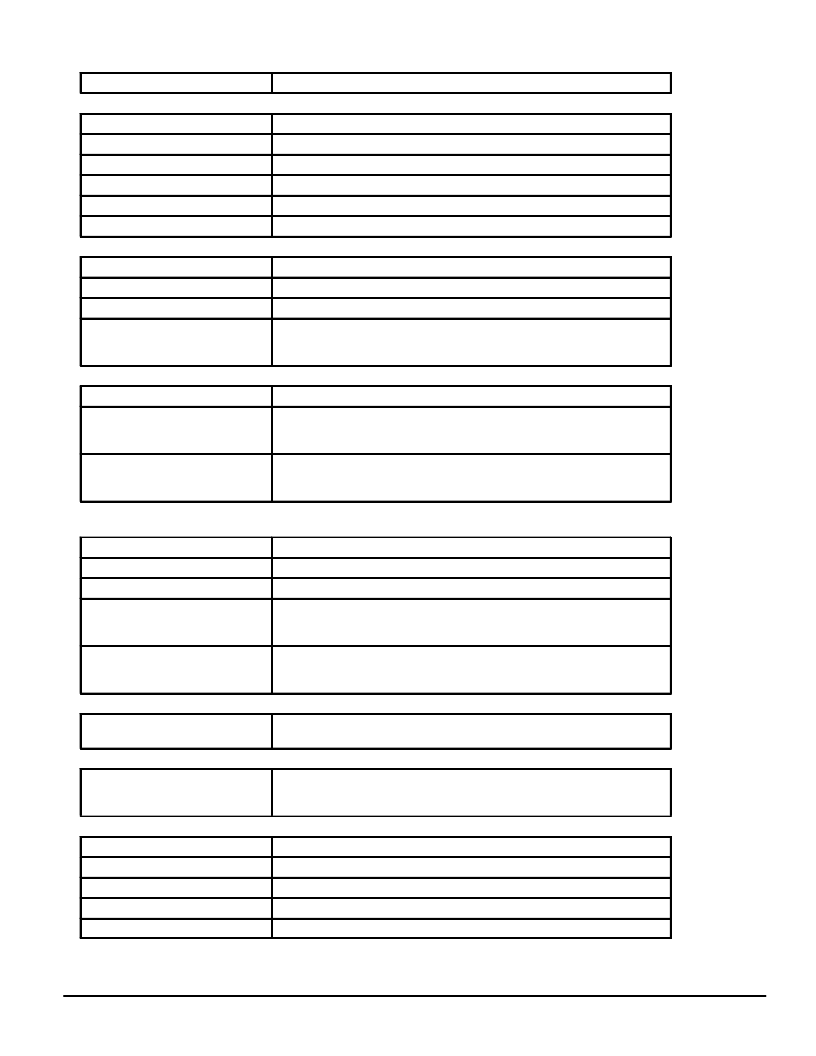

AC AND TIMING CHARACTERISTICS

Parameter

Conditions

Composite Video Input

Amplitude:

1.0 Vp–p,

±

3 dB

Polarity:

Sync tips negative

Bandwidth:

600 kHz

Signal Type:

Interlaced

Max Input R:

470

DC Offset:

Signal to be ac coupled with a minimum series capacitance of 0.1

μ

F.

Non–Standard Video Signals Must Have the Following Characteristics

Sync Amplitude:

200 mV min

Vert Pulse Width:

3H

±

0.5H

Vert Pulse Tilt:

20 mV max

H Timing:

Phase Step (head switch)

±

10

μ

s max

Fh Deviation (long term)

±

0.5% max

Fh p–p Deviation (short term)

±

0.3% max

Horizontal Signal Input (Preferably H Flyback)

Amplitude:

CMOS level signal, low

≤

0.2 VCC, high

≥

0.7 VCC

Video Lock Mode:

Polarity:

Frequency:

Any

15,734.263 Hz,

±

3%

HIN Lock Mode:

Polarity:

Frequency:

Any

Display HFB pulse

Line 21 Input Parameters ( at 1.0 Vp–p)

(Line 21 must be in its proper position to the leading edge of the vertical sync signal.)

Code Amplitude:

50 IRE

±

10 IRE

Code Zero Level:

– 5 IRE, + 15 IRE relative to back porch

Bit Rate:

32 x Fh

10.5

±

1.0

μ

s

(Measured from the midpoint of the leading edge of video H pulse to the midpoint

of the rising edge of the first clock run–in cycle.)

Start of Code:

Start of Data:

3.972

μ

s, – 0.00

μ

s, + 0.30

μ

s

(Measured from the midpoint of the falling edge of the last clock run–in cycle to the

midpoint of the rising edge of the start bit.)

Input Signal–to–Random Noise Performance

Unit will function down to a 25 dB ratio

(CCIR weighted

One error per row or better at that level.

Internal Sync Circuits

The internal sync circuits will lock to

all 525 line or 625 line signals having

a vertical sync pulse.

It is at least 2 H long.

It starts at the proper 2 H boundary for its field.

If equalizing pulse serrations are present they must be less than 0.125 H in width.

Timing Signals

Dot Clock:

768 x FH = 12.0839 MHz

82.75 ns

Dot Period:

Character Cell Width:

1.324

μ

s (tH

÷

48)

45.018

μ

s (34 chars = 17/24 x tH)

42.370

μ

s (32 chars = 2/3 x tH)

Width of Row (Box):

Width of Row (Char):

相关PDF资料 |

PDF描述 |

|---|---|

| MC14415DW | Digital Signal Processors 40-CDIP SB -55 to 125 |

| MC14415FL | Quad Precision Timer/Driver |

| MC14415FP | Quad Precision Timer/Driver |

| MC14415VL | Digital Signal Processors 68-CPGA -55 to 125 |

| MC14415VP | Digital Signal Processors 68-LCCC -55 to 125 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC14415FP | 制造商:Motorola Inc 功能描述: |

| MC14416P | 制造商:Motorola Inc 功能描述: 制造商:Motorola Inc 功能描述:TIME-SLOT ASSIGNER, 22 Pin, Plastic, DIP |

| MC14419P | 制造商:Motorola Inc 功能描述:ENCODER, 16 Pin, Plastic, DIP |

| MC14433P | 制造商:Motorola Inc 功能描述: |

| MC1443G | 制造商:Motorola Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。