- 您现在的位置:买卖IC网 > PDF目录45277 > MC8640DHX1250HE (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1250 MHz, MICROPROCESSOR, CBGA1023 PDF资料下载

参数资料

| 型号: | MC8640DHX1250HE |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 1250 MHz, MICROPROCESSOR, CBGA1023 |

| 封装: | 33 X 33 MM, CERAMIC, FCBGA-1023 |

| 文件页数: | 88/130页 |

| 文件大小: | 1495K |

| 代理商: | MC8640DHX1250HE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页当前第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页

MPC8640 and MPC8640D Integrated Host Processor Hardware Specifications, Rev. 3

60

Freescale Semiconductor

High-Speed Serial Interfaces (HSSI)

13.2.1

SerDes Reference Clock Receiver Characteristics

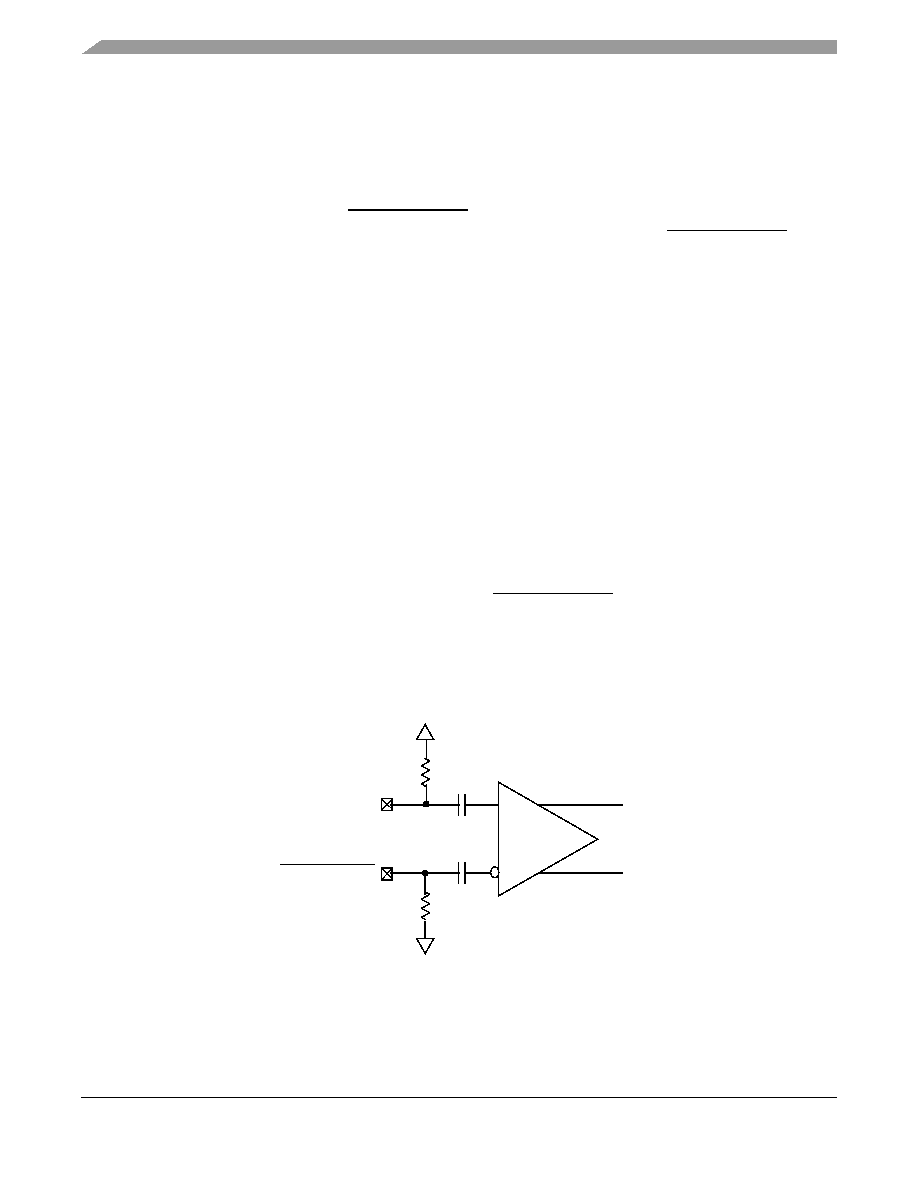

Figure 39 shows a receiver reference diagram of the SerDes reference clocks.

SerDes Reference Clock Receiver Reference Circuit Structure

—The SDn_REF_CLK and SDn_REF_CLK are internally AC-coupled differential inputs as

shown in Figure 39. Each differential clock input (SDn_REF_CLK or SDn_REF_CLK) has a

50-

Ω termination to SGND followed by on-chip AC-coupling.

— The external reference clock driver must be able to drive this termination.

— The SerDes reference clock input can be either differential or single-ended. Refer to the

Differential Mode and Single-ended Mode description below for further detailed requirements.

The maximum average current requirement that also determines the common mode voltage range

— When the SerDes reference clock differential inputs are DC coupled externally with the clock

driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the

exact common mode input voltage is not critical as long as it is within the range allowed by the

maximum average current of 8 mA (refer to the following bullet for more detail), since the

input is AC-coupled on-chip.

— This current limitation sets the maximum common mode input voltage to be less than 0.4 V

(0.4 V

÷ 50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND. For

example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven

by its current source from 0 mA to 16 mA (0–0.8 V), such that each phase of the differential

input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

— If the device driving the SDn_REF_CLK and SDn_REF_CLK inputs cannot drive 50

Ω to

SGND DC, or it exceeds the maximum input current limitations, then it must be AC-coupled

off-chip.

The input amplitude requirement

— This requirement is described in detail in the following sections.

Figure 39. Receiver of SerDes Reference Clocks

Input

Amp

50 W

SD

n_REF_CLK

SD

n_REF_CLK

相关PDF资料 |

PDF描述 |

|---|---|

| MC8640DHX1067NC | 32-BIT, 1067 MHz, MICROPROCESSOR, CBGA1023 |

| MC8640DTVU1000HE | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA1023 |

| MC8640DTHX1067NC | 32-BIT, 1067 MHz, MICROPROCESSOR, CBGA1023 |

| MC8640THX1250HC | 32-BIT, 1250 MHz, MICROPROCESSOR, CBGA1023 |

| MC8640DTVU1250HE | 32-BIT, 1250 MHz, MICROPROCESSOR, CBGA1023 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC8640DHX1250N | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications Addendum for the MC8640xTxxyyyyaC Series |

| MC8640DTHX1000H | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications |

| MC8640DTHX1000HC | 功能描述:微处理器 - MPU G8 REV2.1 1.05V -40/105C RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MC8640DTHX1000HE | 功能描述:微处理器 - MPU G8 REV 3.0 1.05V -40/105C RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MC8640DTHX1000N | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications Addendum for the MC8640xTxxyyyyaC Series |

发布紧急采购,3分钟左右您将得到回复。