- 您现在的位置:买卖IC网 > PDF目录189448 > OR3L165B8PS208-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1024 CLBS, 120000 GATES, 333 MHz, PQFP208 PDF资料下载

参数资料

| 型号: | OR3L165B8PS208-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1024 CLBS, 120000 GATES, 333 MHz, PQFP208 |

| 封装: | SQFP2-208 |

| 文件页数: | 39/77页 |

| 文件大小: | 873K |

| 代理商: | OR3L165B8PS208-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页

44

PD78052, 78053, 78054, 78055, 78056, 78058

Data Sheet U12327EJ5V0DS00

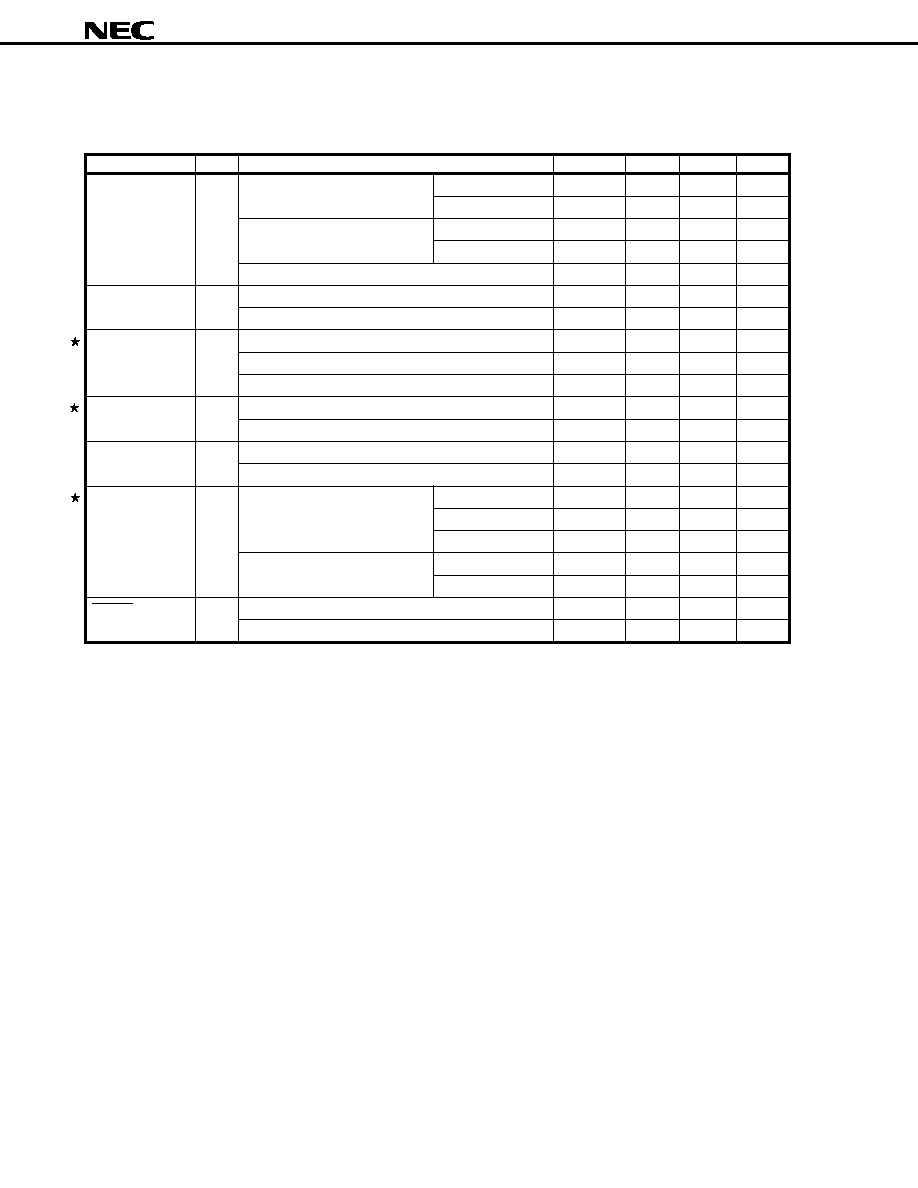

AC Characteristics

(1) Basic operation (TA = –40 to +85

°C, VDD = 2.0 to 6.0 V)

Parameter

Symbol

Conditions

MIN.

TYP.

MAX.

Unit

Cycle time

TCY

Operating with main system clock VDD = 2.7 to 6.0 V

0.8

64

s

(minimum

(fXX = 2.5 MHz)Note 1

2.2

64

s

instruction

Operating with main system clock 4.5 V

≤ VDD ≤ 6.0 V

0.4

32

s

execution time)

(fXX = 5.0 MHz)Note 2

2.7 V

≤ VDD < 4.5 V

0.8

32

s

Operating with subsystem clock

40Note 3

122

125

s

TI00, TI01, TI1, TI2

fTI

VDD = 4.5 to 6.0 V

0

4

MHz

input frequency

0

275

kHz

TI00 input high-/

tTIH,

3.5 V

≤ VDD ≤ 6.0 V

2/fsam + 0.1Note 4

s

low-level width

tTIL

2.7 V

≤ VDD < 3.5 V

2/fsam + 0.2Note 4

s

2/fsam + 0.5Note 4

s

TI01 input high-/

tTIH,VDD = 4.5 to 6.0 V

10

s

low-level width

tTIL

20

s

TI1, TI2 input high-/ tTIH,VDD = 4.5 to 6.0 V

100

ns

low-level width

tTIL

1.8

s

Interrupt request

tINTH,

INTP0

3.5 V

≤ VDD ≤ 6.0 V 2/fsam + 0.1Note 4

s

input high-/

tINTL

2.7 V

≤ VDD < 3.5 V 2/fsam + 0.2Note 4

s

low-level width

2/fsam + 0.5Note 4

s

INTP1 to INTP6, KR0 to KR7

VDD = 2.7 to 6.0 V

10

s

20

s

RESET

tRSL

VDD = 2.7 to 6.0 V

10

s

low-level width

20

s

Notes 1. Operation with main system clock fXX = fX/2 (when the oscillation mode selection register (OSMS) is set

to 00H)

2. Operation with main system clock fXX = fX (when OSMS is set to 01H)

3. Value when an external clock is used. When a crystal resonator is used, it is 114

s (MIN.).

4. Selection of fsam = fXX/2N, fXX/32, fXX/64, fXX/128 is possible with bits 0 and 1 (SCS0, SCS1) of the sampling

clock selection register (SCS) (when N= 0 to 4).

相关PDF资料 |

PDF描述 |

|---|---|

| OR3L225B7PS432-DB | FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA432 |

| OR3L225B7PS432I-DB | FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA432 |

| OR3L225B7PS680-DB | FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA680 |

| OR3L225B7PS680I-DB | FPGA, 1444 CLBS, 166000 GATES, 266.4 MHz, PBGA680 |

| OR3L225B8PS432-DB | FPGA, 1444 CLBS, 166000 GATES, 333 MHz, PBGA432 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR3L165B8PS240-DB | 功能描述:FPGA - 现场可编程门阵列 8192 LUT 516 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3L225B7BC432-DB | 功能描述:FPGA - 现场可编程门阵列 11552 LUT 612 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3L225B7BC432I-DB | 功能描述:FPGA - 现场可编程门阵列 11552 LUT 612 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3L225B7BM680-DB | 功能描述:FPGA - 现场可编程门阵列 11552 LUT 612 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3L225B7BM680I-DB | 功能描述:FPGA - 现场可编程门阵列 11552 LUT 612 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。