- 您现在的位置:买卖IC网 > PDF目录191942 > QL5064-33APB456M (QUICKLOGIC CORP) PCI BUS CONTROLLER, PBGA456 PDF资料下载

参数资料

| 型号: | QL5064-33APB456M |

| 厂商: | QUICKLOGIC CORP |

| 元件分类: | 总线控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA456 |

| 封装: | PLASTIC, BGA-456 |

| 文件页数: | 8/45页 |

| 文件大小: | 635K |

| 代理商: | QL5064-33APB456M |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

2006 QuickLogic Corporation

QL5064 QuickPCI Data Sheet Rev. I

16

PCI Back-End Interface Signals

The PCI back-end internal signals can interface directly to pins or to internal logic cells or RAM blocks in the

programmable logic region of the device. These signals are used to customize the device so that it can connect

to other devices on the board directly, without any glue-logic required.

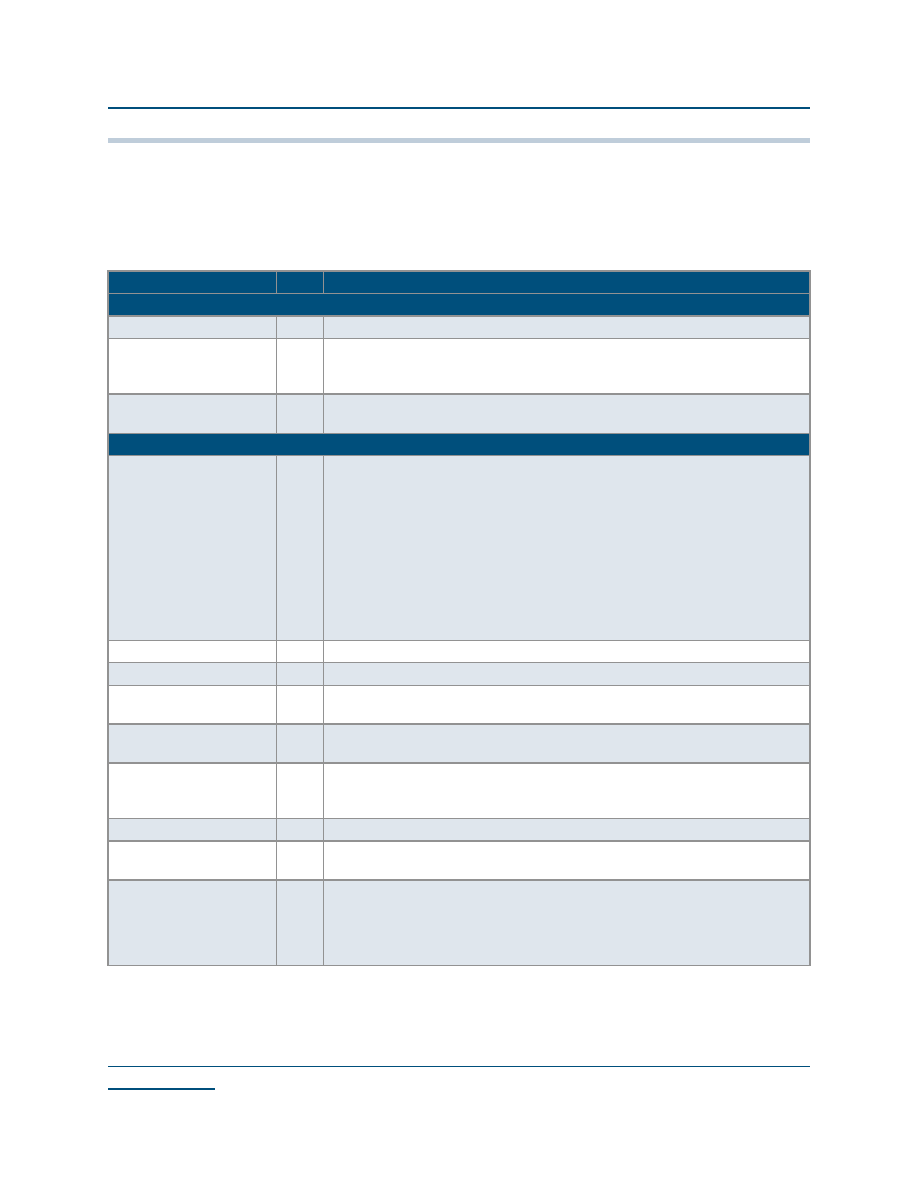

Table 2: PCI Back-End Interface Signals

Symbol

I/Oa

Description

Clocks

pci_clk_2fpga

I

Buffered version of the PCI clock. For use in the FPGA.

user_clk

O

FPGA supplied clock used for all interface to the embedded PCI core. This signal

is required and all communication between the embedded PCI core and the FPGA

is synchronous to this clock with the exception of the DMA arbitrary signals.

fpga_reset

I

Active High. Global reset signal from the PCI core. Active High. This signal should

be used as the global reset for the FPGA and all other supporting circuitry.

Target Interface

user_region [2:0]

I

When target_addr_valid is active, these signals indicate which of the following

regions are being accessed.

3’b000 BAR0

3’b001 BAR1

3’b010 BAR2

3’b011 BAR3

3’b100 BAR4

3’b101 BAR5

3’b110 Expansion ROM

3’b111 Configuration Space 0x40-0xff

user_stop

O

Active High. Stops prefetch after the current cycle.

user_be_req [7:0]

I

Active High. Byte lanes requested by PCI for all target accesses.

user_rdwr

I

When target_addr_valid is active, a logic ‘1’ indicates that the requested

transaction is a read. When ‘0’ the present transaction is a write.

user_addr_valid

I

Active High. Indicates that PCI is requesting a sequentially continuing target

access.

user_req

I

Active High. When active, PCI is requesting at least one piece of data to be

transferred. Deasserted after an advance generated by a read or write from the

target FIFOs or after ‘target_user_stop’ is asserted.

user_mult

I

Active High. PCI is requesting at least 2+ pieces of data to be transferred.

user_addr_output [32:0]

I

The current address of the PCI target transaction. Incremented automatically by a

quad word when a 64-bit piece of target data is written or read.

addr_select

O

Selects which half of the 64-bit PCI address for a target transaction is placed on

the user_addr [32:0] bus.

0 - [35:3]

1 - 00000. [63:36]

相关PDF资料 |

PDF描述 |

|---|---|

| QL5064-66APB456M | PCI BUS CONTROLLER, PBGA456 |

| QL5064-66APBN456C | PCI BUS CONTROLLER, PBGA456 |

| QL5064-66BPBN456M | PCI BUS CONTROLLER, PBGA456 |

| QL5064-75CPBN456I | PCI BUS CONTROLLER, PBGA456 |

| QL5064-75CPS484C | PCI BUS CONTROLLER, PBGA484 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL5064-66APS484C-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66APS484I-5541 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-66BPS484C-5725 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484C-5616 | 制造商:QuickLogic Corporation 功能描述: |

| QL5064-75CPS484I-5612 | 制造商:QuickLogic Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。