- 您现在的位置:买卖IC网 > PDF目录69322 > RK80532KE056512 (INTEL CORP) 32-BIT, 2400 MHz, MICROPROCESSOR, CPGA604 PDF资料下载

参数资料

| 型号: | RK80532KE056512 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 2400 MHz, MICROPROCESSOR, CPGA604 |

| 封装: | FLIP CHIP, MICRO, PGA2-604 |

| 文件页数: | 60/102页 |

| 文件大小: | 1464K |

| 代理商: | RK80532KE056512 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页当前第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页

60

Intel Xeon Processor with 533 MHz Front Side Bus at 2 GHz to 3.06 GHz

4.2

Signal Definitions

Table 41. Signal Definitions (Sheet 1 of 9)

Name

Type

Description

Notes

A[35:3]#

I/O

A[35:3]# (Address) define a 236 byte physical memory address space. In sub-phase

1 of the address phase, these pins transmit the address of a transaction. In sub-

phase 2, these pins transmit transaction type information. These signals must

connect the appropriate pins of all agents on the front side bus. A[35:3]# are

protected by parity signals AP[1:0]#. A[35:3]# are source synchronous signals and

are latched into the receiving buffers by ADSTB[1:0]#.

On the active-to-inactive transition of RESET#, the processors sample a subset of

the A[35:3]# pins to determine their power-on configuration. See Section 6.1.

4

A20M#

I

If A20M# (Address-20 Mask) is asserted, the processor masks physical address bit

20 (A20#) before looking up a line in any internal cache and before driving a read/

write transaction on the bus. Asserting A20M# emulates the 8086 processor's

address wrap-around at the 1 MByte boundary. Assertion of A20M# is only

supported in real mode.

A20M# is an asynchronous signal. However, to ensure recognition of this signal

following an I/O write instruction, it must be valid along with the TRDY# assertion of

the corresponding I/O write bus transaction.

3

ADS#

I/O

ADS# (Address Strobe) is asserted to indicate the validity of the transaction

address on the A[35:3]# pins. All bus agents observe the ADS# activation to begin

parity checking, protocol checking, address decode, internal snoop, or deferred

reply ID match operations associated with the new transaction. This signal must

connect the appropriate pins on all front side bus agents.

4

ADSTB[1:0]#

I/O

Address strobes are used to latch A[35:3]# and REQ[4:0]# on their rising and falling

edge.

4

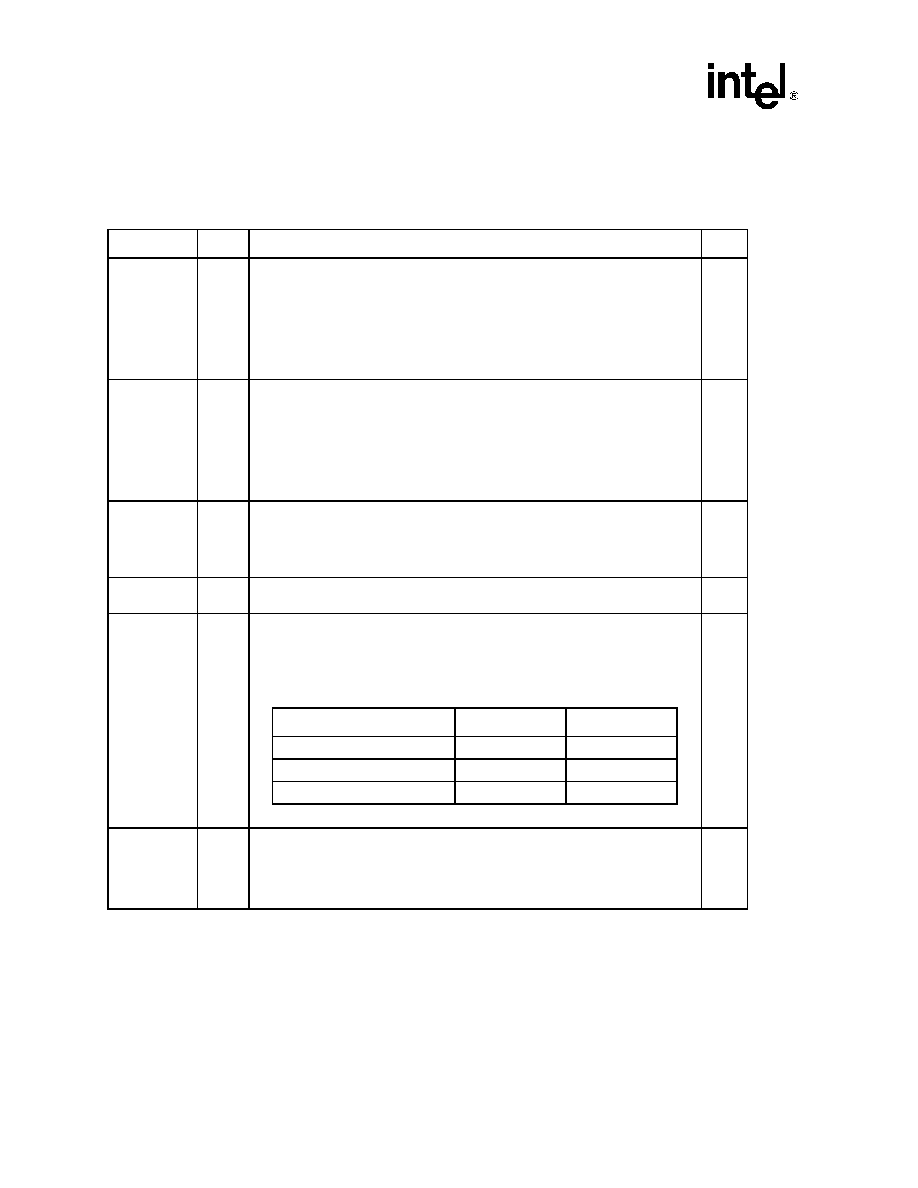

AP[1:0]#

I/O

AP[1:0]# (Address Parity) are driven by the request initiator along with ADS#,

A[35:3]#, and the transaction type on the REQ[4:0]# pins. A correct parity signal is

high if an even number of covered signals are low and low if an odd number of

covered signals are low. This allows parity to be high when all the covered signals

are high. AP[1:0]# should connect the appropriate pins of all front side bus agents.

The following table defines the coverage model of these signals.

4

BCLK[1:0]

I

The differential pair BCLK (Bus Clock) determines the bus frequency. All processor

front side bus agents must receive these signals to drive their outputs and latch

their inputs.

All external timing parameters are specified with respect to the rising edge of

BCLK0 crossing the falling edge of BCLK1.

4

Request Signals

Subphase 1

Subphase 2

A[35:24]#

AP0#

AP1#

A[23:3]#

AP1#

AP0#

REQ[4:0]#

AP1#

AP0#

相关PDF资料 |

PDF描述 |

|---|---|

| BX80532KE3060D | 3060 MHz, MICROPROCESSOR, XMA |

| BX80532KE2400DU | 2400 MHz, MICROPROCESSOR, XMA604 |

| RK80532PG072512 | 2800 MHz, MICROPROCESSOR, PGA478 |

| RK80532RC049128 | 32-BIT, 2100 MHz, MICROPROCESSOR, CPGA478 |

| RK80532RC056128 | 2400 MHz, MICROPROCESSOR, CPGA478 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RK80532KE056512S L6GD | 功能描述:IC XEON 2.4GHZ INT-MPGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:- 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| RK80532KE056512S L6VL | 制造商:Intel 功能描述:MPU Xeon 制造商:Intel 功能描述:PRESTONIA; MPU XEON NETBURST 64BIT 0.13UM 2.4GHZ 604PIN - Trays |

| RK80532KE056512S L72D | 制造商:Intel 功能描述:MPU Xeon? Processor 64-Bit 0.13um 2.4GHz 604-Pin FCPGA |

| RK80532KE056512SL73L | 功能描述:IC XEON 2.4GHZ 604FC-MPGA-2P RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:- 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| RK80532KE067512 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。