- 您现在的位置:买卖IC网 > PDF目录225240 > ST72F652R4T1 (STMICROELECTRONICS) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | ST72F652R4T1 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP64 |

| 封装: | 14 X 14 MM, TQFP-64 |

| 文件页数: | 99/160页 |

| 文件大小: | 974K |

| 代理商: | ST72F652R4T1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页当前第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页

ST7265

43/160

INTERRUPTS (Cont’d)

7.5 INTERRUPT REGISTER DESCRIPTION

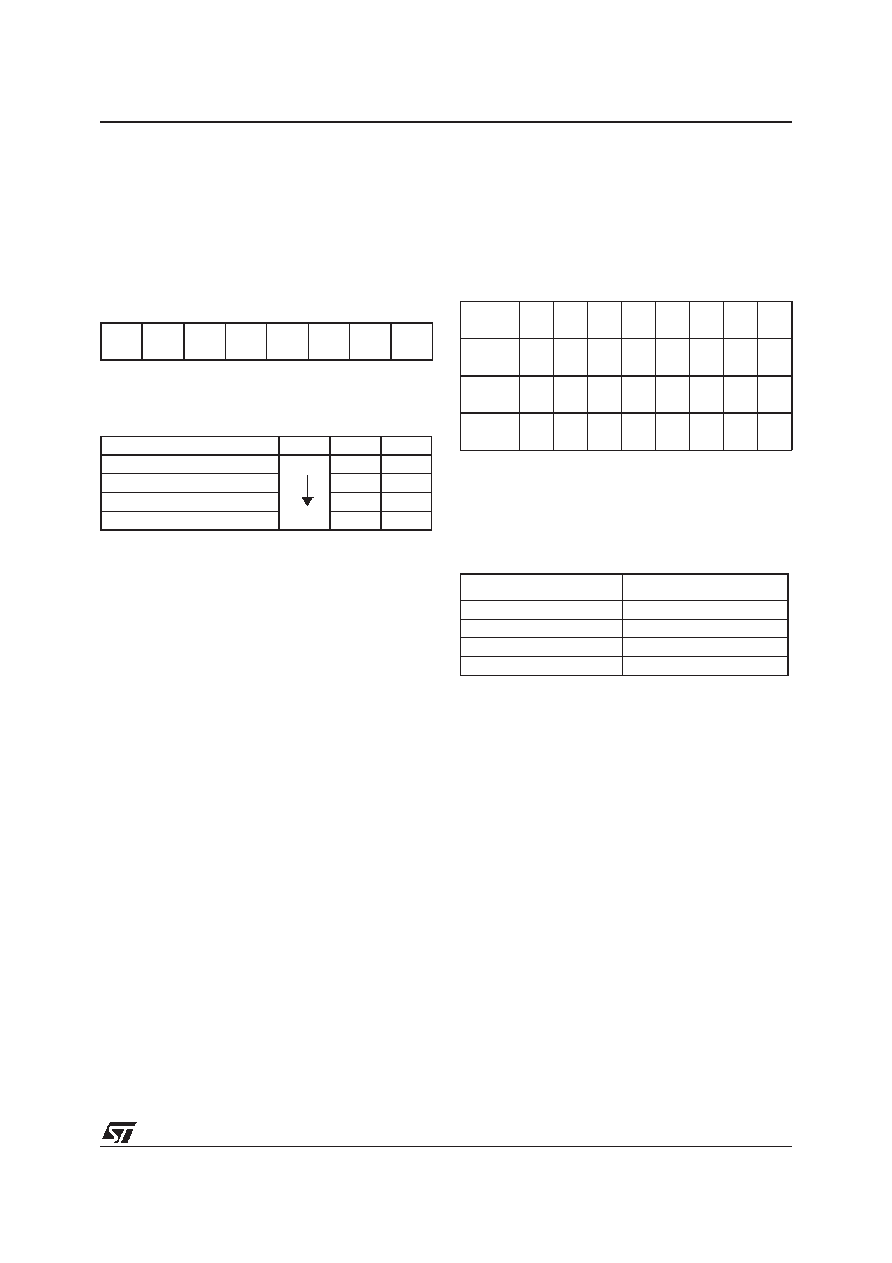

CPU CC REGISTER INTERRUPT BITS

Read/Write

Reset Value: 111x 1010 (xAh)

Bit 5, 3 = I1, I0

Software Interrupt Priority

These two bits indicate the current interrupt soft-

ware priority.

These two bits are set/cleared by hardware when

entering in interrupt. The loaded value is given by

the corresponding bits in the interrupt software pri-

ority registers (ISPRx).

They can be also set/cleared by software with the

RIM, SIM, HALT, WFI, IRET and PUSH/POP in-

structions (see “Interrupt Dedicated Instruction

Set” table).

*Note: TLI, TRAP and RESET events are non

maskable sources and can interrupt a level 3 pro-

gram.

INTERRUPT SOFTWARE PRIORITY REGIS-

TERS (ISPRX)

Read/Write (bit 7:4 of ISPR3 are read only)

Reset Value: 1111 1111 (FFh)

These four registers contain the interrupt software

priority of each interrupt vector.

– Each interrupt vector (except RESET and TRAP)

has corresponding bits in these registers where

its own software priority is stored. This corre-

spondance is shown in the following table.

– Each I1_x and I0_x bit value in the ISPRx regis-

ters has the same meaning as the I1 and I0 bits

in the CC register.

– Level 0 can not be written (I1_x=1, I0_x=0). In

this case, the previously stored value is kept. (ex-

ample: previous=CFh, write=64h, result=44h)

The RESET, TRAP and TLI vectors have no soft-

ware priorities. When one is serviced, the I1 and I0

bits of the CC register are both set.

*Note: Bits in the ISPRx registers which corre-

spond to the TLI can be read and written but they

are not significant in the interrupt process man-

agement.

Caution: If the I1_x and I0_x bits are modified

while the interrupt x is executed the following be-

haviour has to be considered: If the interrupt x is

still pending (new interrupt or flag not cleared) and

the new software priority is higher than the previ-

ous one, the interrupt x is re-entered. Otherwise,

the software priority stays unchanged up to the

next interrupt request (after the IRET of the inter-

rupt x).

70

11

I1

H

I0

NZ

C

Interrupt Software Priority

Level

I1

I0

Level 0 (main)

Low

High

10

Level 1

0

1

Level 2

0

Level 3 (= interrupt disable*)

1

70

ISPR0

I1_3

I0_3

I1_2

I0_2

I1_1

I0_1

I1_0

I0_0

ISPR1

I1_7

I0_7

I1_6

I0_6

I1_5

I0_5

I1_4

I0_4

ISPR2

I1_11 I0_11 I1_10 I0_10 I1_9

I0_9

I1_8

I0_8

ISPR3

1111

I1_13 I0_13 I1_12 I0_12

Vector address

ISPRx bits

FFFB h-FFFAh

I1_0 and I0_0 bits*

FFF9h-FFF8h

I1_1 and I0_1 bits

...

FFE1h-FFE0h

I1_13 and I0_13 bits

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST733C04LHK1L | 1900 A, 400 V, SCR, TO-200AC |

| ST733C04LHK3 | 1900 A, 400 V, SCR, TO-200AC |

| ST7PLITE09Y0U6TR | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, QCC20 |

| STARX032XXEEXF120.0 | INTERVAL-DELAY RELAY, DPDT, MOMENTARY, 24VDC (COIL), 3000mW (COIL), 10A (CONTACT), 28VDC (CONTACT), 120s, SOCKET MOUNT |

| STARX032XXEEXF4.000 | INTERVAL-DELAY RELAY, DPDT, MOMENTARY, 24VDC (COIL), 3000mW (COIL), 10A (CONTACT), 28VDC (CONTACT), 4s, SOCKET MOUNT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72P262M6/OZXTR | 制造商:STMicroelectronics 功能描述:ST72P262M6/OZXTR |

| ST72P324TA/OBZTR | 制造商:STMicroelectronics 功能描述: |

| ST72P324TA/OHXTR | 制造商:STMicroelectronics 功能描述: |

| ST72P4T128M-A05AU | 制造商:STEC Inc 功能描述:1GB,ECC,REG,DDR2-400,UNLEAD - Bulk |

| ST72T101G1B6 | 功能描述:8位微控制器 -MCU OTP EPROM 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。