参数资料

| 型号: | XC3S1400A-4FT256I |

| 厂商: | Xilinx Inc |

| 文件页数: | 93/132页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN 3 256FTBGA |

| 标准包装: | 90 |

| 系列: | Spartan®-3A |

| LAB/CLB数: | 2816 |

| 逻辑元件/单元数: | 25344 |

| RAM 位总计: | 589824 |

| 输入/输出数: | 161 |

| 门数: | 1400000 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页当前第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页

DC and Switching Characteristics

DS529-3 (v2.0) August 19, 2010

63

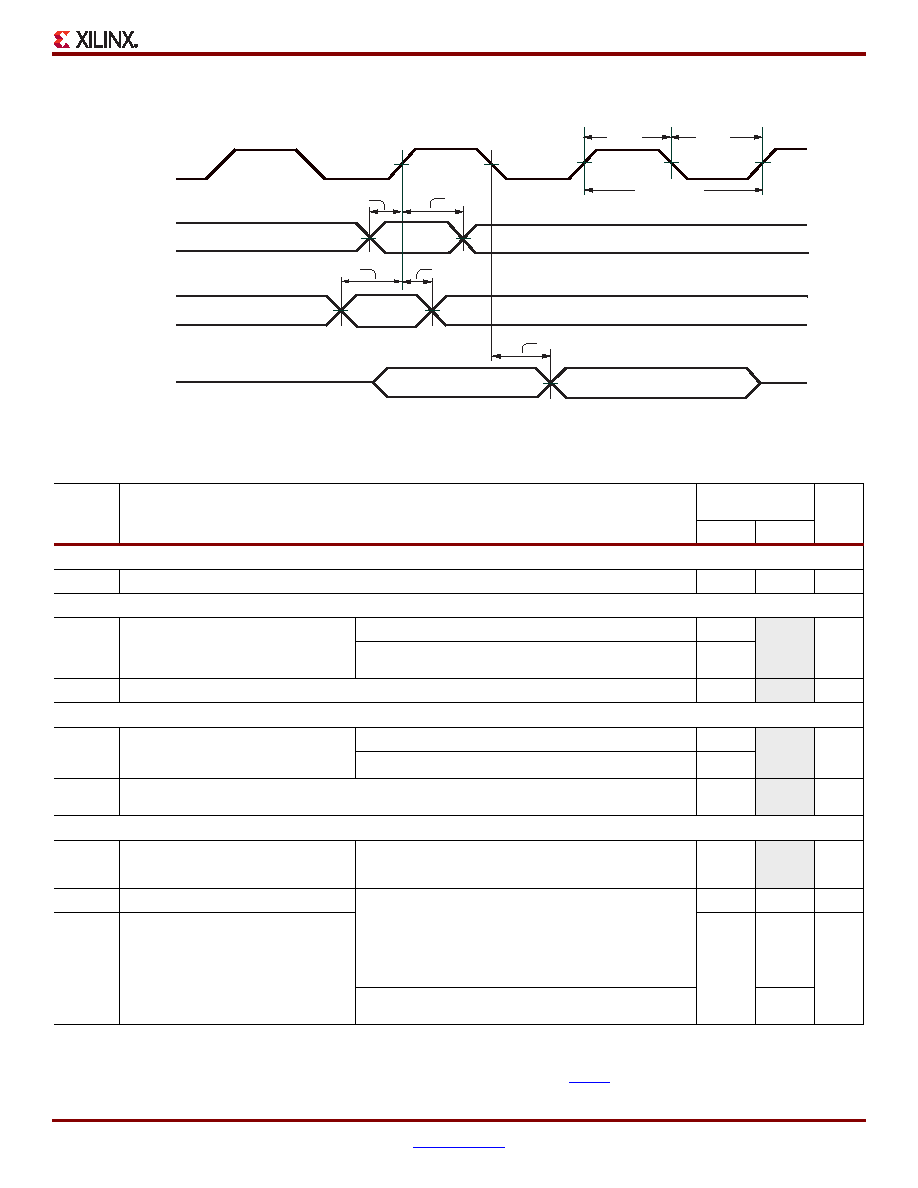

IEEE 1149.1/1532 JTAG Test Access Port Timing

Figure 16: JTAG Waveforms

Table 56: Timing for the JTAG Test Access Port

Symbol

Description

All Speed

Grades

Units

Min

Max

Clock-to-Output Times

TTCKTDO The time from the falling transition on the TCK pin to data appearing at the TDO pin

1.0

11.0

ns

Setup Times

TTDITCK

The time from the setup of data at the

TDI pin to the rising transition at the

TCK pin

All devices and functions except those shown below

7.0

–ns

Boundary scan commands (INTEST, EXTEST,

SAMPLE) on XC3S700A and XC3S1400A FPGAs

11.0

TTMSTCK The time from the setup of a logic level at the TMS pin to the rising transition at the TCK pin

7.0

–ns

Hold Times

TTCKTDI

The time from the rising transition at

the TCK pin to the point when data is

last held at the TDI pin

All functions except those shown below

0

–ns

Configuration commands (CFG_IN, ISC_PROGRAM)

2.0

TTCKTMS The time from the rising transition at the TCK pin to the point when a logic level is last held at the

TMS pin

0

–ns

Clock Timing

TCCH

The High pulse width at the TCK pin

All functions except ISC_DNA command

5

–ns

TCCL

The Low pulse width at the TCK pin

5

–ns

TCCHDNA The High pulse width at the TCK pin

During ISC_DNA command

10

10,000

ns

TCCLDNA The Low pulse width at the TCK pin

10

10,000

ns

FTCK

Frequency of the TCK signal

All operations on XC3S50A, XC3S200A, and

XC3S400A FPGAs and for BYPASS or HIGHZ

instructions on all FPGAs

033

MHz

All operations on XC3S700A and XC3S1400A FPGAs,

except for BYPASS or HIGHZ instructions

20

Notes:

1.

The numbers in this table are based on the operating conditions set forth in Table 8.

2.

For details on JTAG see Chapter 9 “JTAG Configuration Mode and Boundary-Scan” in UG332 Spartan-3 Generation Configuration User

Guide.

TCK

TTMSTCK

TMS

TDI

TDO

(Input)

(Output)

TTCKTMS

TTCKTDI

TTCKTDO

TTDITCK

DS099_06_020709

TCCH

TCCL

1/FTCK

相关PDF资料 |

PDF描述 |

|---|---|

| XC3S1400A-5FGG676C | IC SPARTAN-3A FPGA 1400K 676FBGA |

| XC3S1400AN-4FGG676I | IC FPGA SPARTAN-AN 1400K 676FBGA |

| XC3S1600E-5FGG484C | IC FPGA SPARTAN-3E 1600K 484FBGA |

| XC3S400AN-4FG400I | IC FPGA SPARTAN 3AN 400FBGA |

| XC3SD1800A-4CSG484LI | IC FPGA SPARTAN 3 DSP 484CSGBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC3S1400A-4FTG256C | 功能描述:IC FPGA SPARTAN3A 1400K 256FTBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S1400A-4FTG256I | 功能描述:IC FPGA SPARTAN3A 1400K 256FTBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S1400A-5FG484C | 功能描述:IC SPARTAN-3A FPGA 1400K 484FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S1400A-5FG676C | 功能描述:IC SPARTAN-3A FPGA 1400K 676FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC3S1400A-5FGG484C | 功能描述:IC SPARTAN-3A FPGA 1400K 484FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-3A 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。