参数资料

| 型号: | XCF128XFTG64C |

| 厂商: | Xilinx Inc |

| 文件页数: | 52/88页 |

| 文件大小: | 0K |

| 描述: | IC PROM SRL 128M GATE 64-FTBGA |

| 标准包装: | 1 |

| 可编程类型: | 系统内可编程 |

| 存储容量: | 128Mb |

| 电源电压: | 1.7 V ~ 2 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 64-TBGA |

| 供应商设备封装: | 64-TFBGA |

| 包装: | 托盘 |

| 产品目录页面: | 601 (CN2011-ZH PDF) |

| 其它名称: | 122-1578 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

Platform Flash XL High-Density Configuration and Storage Device

DS617 (v3.0.1) January 07, 2010

Product Specification

56

R

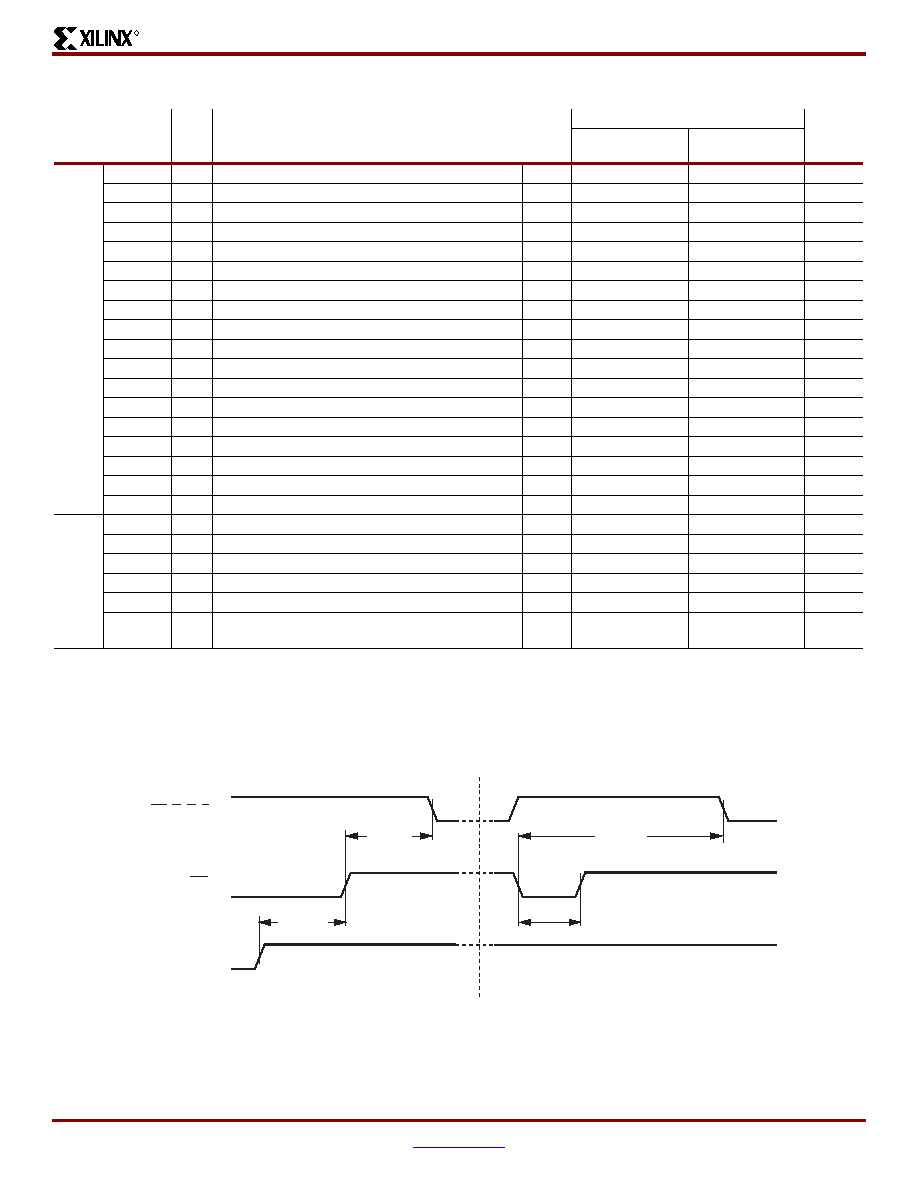

Table 31: Write AC Characteristics, Chip Enable Controlled(1)

Symbol

Alt

Parameter

Voltage Range

Unit

VDDQ =

2.3V to 2.7V

VDDQ =

3.0V to 3.6V

C

h

ip

En

ab

le

C

o

n

tr

o

ll

ed

T

imi

n

g

s

TAVAV

TWC Address Valid to Next Address Valid

Min

85

ns

TAVEH

Address Valid to Chip Enable High

Min

50

ns

TAVLH

Address Valid to Latch Enable High

Min

10

ns

TDVEH

TDS

Data Valid to Chip Enable High

Min

50

ns

TEHAX

TAH

Chip Enable High to Address Transition

Min

0

ns

TEHDX

TDH

Chip Enable High to Input Transition

Min

0

ns

TEHEL

TCPH Chip Enable High to Chip Enable Low

Min

25

ns

TEHGL

Chip Enable High to Output Enable Low

Min

0

ns

TEHWH

TCH

Chip Enable High to Write Enable High

Min

0

ns

TELKV

Chip Enable Low to Clock Valid

Min

9

ns

TELEH

TCP

Chip Enable Low to Chip Enable High

Min

50

ns

TELLH

Chip Enable Low to Latch Enable High

Min

10

ns

TELQV

Chip Enable Low to Output Valid

Min

85

ns

TGHEL

Output Enable High to Chip Enable Low

Min

17

ns

TLHAX

Latch Enable High to Address Transition

Min

9

ns

TLLLH

Latch Enable Pulse Width

Min

10

ns

TWHEL(2)

Write Enable High to Chip Enable Low

Min

25

ns

TWLEL

TCS

Write Enable Low to Chip Enable Low

Min

0

ns

Pr

otectio

n

Ti

mi

ng

s

TEHVPL

Chip Enable High to VPP Low

Min

200

ns

TEHWPL

Chip Enable High to Write Protect Low

Min

200

ns

TQVVPL

Output (Status Register) Valid to VPP Low

Min

0

ns

TQVWPL

Output (Status Register) Valid to Write Protect Low

Min

0

ns

TVPHEH

TVPS VPP High to Chip Enable High

Min

200

ns

TWPHEH

Write Protect High to Chip Enable High

Min

200

ns

Notes:

1.

Sampled only, not 100% tested.

2.

TWHEL has this value when reading in the targeted bank or when reading following a Set Configuration Register command. System designers

should take this timing into account and can insert a software No-Op instruction to delay the first read in the same bank after issuing any

command and to delay the first read to any address after issuing a Set Configuration Register command. If the first read after the command

is a Read Array operation in a different bank and no changes to the Configuration Register are issued, TWHEL is 0 ns.

X-Ref Target - Figure 33

Figure 33: Reset and Power-Up AC Waveforms

RP

V

DD

, V

DDQ

T

VDHPH

T

PLPH

T

PLWL

T

PLEL

T

PLGL

T

PLLL

T

PHWL

T

PHEL

T

PHGL

T

PHLL

e

R

p

U

-

r

e

w

o

P

set

W,E,G,L

DS617_50_090108

相关PDF资料 |

PDF描述 |

|---|---|

| XCF32PFS48C | IC PROM SRL 1.8V 32M 48CSBGA |

| XCR3256XL-7CS280C | IC CPLD 256MCELL 3.3V HP 280CSP |

| XCS10-3VQG100C | IC FPGA 5V C-TEMP 100-VQFP |

| XCV600E-8HQ240C | IC FPGA 1.8V C-TEMP 240-HQFP |

| XCV812E-8FG900C | IC FPGA 1.8V C-TEMP 900-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCF128XFTG64CES | 制造商:Xilinx 功能描述: |

| XCF12-L4Z1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-L4Z1 |

| XCF12-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-S1 |

| XCF13-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF13-S1 |

| XCF16P | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMs |

发布紧急采购,3分钟左右您将得到回复。