参数资料

| 型号: | XCF128XFTG64C |

| 厂商: | Xilinx Inc |

| 文件页数: | 83/88页 |

| 文件大小: | 0K |

| 描述: | IC PROM SRL 128M GATE 64-FTBGA |

| 标准包装: | 1 |

| 可编程类型: | 系统内可编程 |

| 存储容量: | 128Mb |

| 电源电压: | 1.7 V ~ 2 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 64-TBGA |

| 供应商设备封装: | 64-TFBGA |

| 包装: | 托盘 |

| 产品目录页面: | 601 (CN2011-ZH PDF) |

| 其它名称: | 122-1578 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页当前第83页第84页第85页第86页第87页第88页

Platform Flash XL High-Density Configuration and Storage Device

DS617 (v3.0.1) January 07, 2010

Product Specification

84

R

Buffer Program in

Erase Suspend

Setup

Buffer Program Load 1 in Erase Suspend (give word count load (N-1))

–

Buffer Load 1

Buffer Program Load 2 in Erase Suspend(7)

Exit

see note (7)

Buffer Load 2

Buffer Program Confirm in Erase Suspend when count =0; Else Buffer Program

Load 2 in Erase Suspend(9)

Confirm

Erase Suspend (sequence error)

Busy

IS in BP busy in ES

Buffer Program Busy in Erase Suspend

ES

IS in BP busy

in ES

BP busy in ES

IS in ES

Suspend

IS in BP suspend in ES

Buffer Program Suspend in Erase Suspend

–

IS in BP

Suspend in ES

Buffer Program Suspend in Erase Suspend

Blank Check

Setup

Ready (error)

–

Blank Check

busy

IS in Blank Check busy

Blank Check busy

Ready

Lock/CR Setup in ES

Erase Suspend

(Lock error)

Erase Suspend

Erase Suspend (Lock error)

–

BEFP

Setup

Ready (error)

–

Busy

BEFP Busy(8)

Exit

BEFP

Busy(8)

–

Notes:

1.

CI = Command Interface: CR = Configuration register: BEFP = Buffer Enhanced Factory program: P/E C = Program/Erase controller: IS =

Illegal State: BP = Buffer program: ES = Erase suspend: WA0 = Address in a block different from first BEFP address.

2.

If the P/E C is active, both cycle are ignored.

3.

BEFP Exit when Block Address is different from first Block Address and data are FFFFh.

4.

Illegal commands are those not defined in the command set.

5.

–: not available. In this case the state remains unchanged.

6.

If N = 0 go to Buffer Program Confirm. Else (not = 0) go to Buffer Program Load 2 (data load)

7.

If N = 0 go to Buffer Program Confirm in Erase suspend. Else (not = 0) go to Buffer Program Load 2 in Erase suspend.

8.

BEFP is allowed only when Status Register bit SR0 is set to '0'. BEFP is busy if Block Address is first BEFP Address. Any other commands

are treated as data.

9.

Buffer Program will fail at this point if any block address is different from the first address

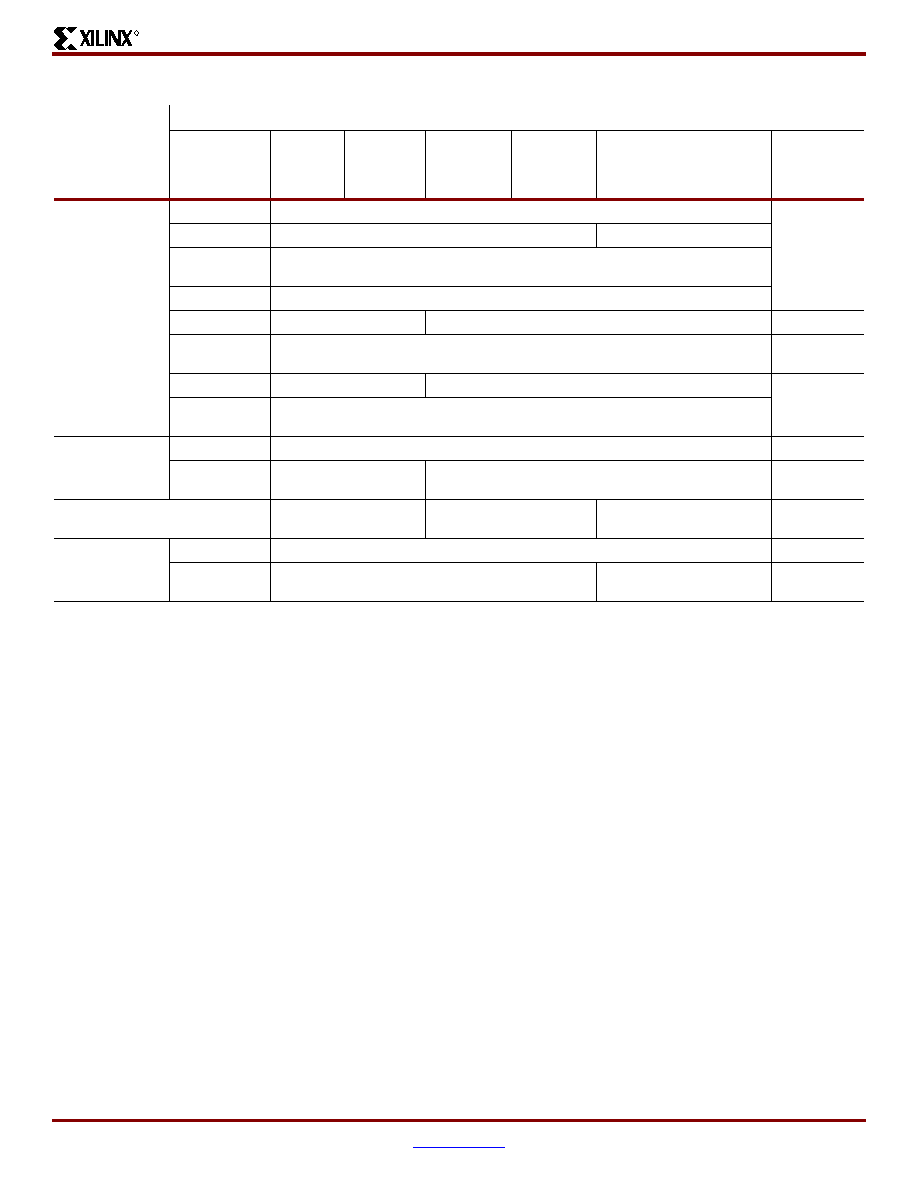

Table 48: Command Interface States – Lock Table, Next State(1) (Cont’d)

Current CI State

Command Input

Lock/CR

Setup(2) (60h)

OTP

Setup(2)

(C0h)

Block

Lock

Confirm

(01h)

Block

Lock-Down

Confirm

(2Fh)

Set CR

Confirm

(03h)

Block

Address

(WA0)(3)

(XXXXh)

Illegal

Command(4)

P/E C

Operation

Completed(5)

相关PDF资料 |

PDF描述 |

|---|---|

| XCF32PFS48C | IC PROM SRL 1.8V 32M 48CSBGA |

| XCR3256XL-7CS280C | IC CPLD 256MCELL 3.3V HP 280CSP |

| XCS10-3VQG100C | IC FPGA 5V C-TEMP 100-VQFP |

| XCV600E-8HQ240C | IC FPGA 1.8V C-TEMP 240-HQFP |

| XCV812E-8FG900C | IC FPGA 1.8V C-TEMP 900-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCF128XFTG64CES | 制造商:Xilinx 功能描述: |

| XCF12-L4Z1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-L4Z1 |

| XCF12-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF12-S1 |

| XCF13-S1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Catalogue / XCF13-S1 |

| XCF16P | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMs |

发布紧急采购,3分钟左右您将得到回复。