- 您现在的位置:买卖IC网 > PDF目录370133 > 7549 (Renesas Technology Corp.) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF资料下载

参数资料

| 型号: | 7549 |

| 厂商: | Renesas Technology Corp. |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 单芯片8位CMOS微机 |

| 文件页数: | 22/73页 |

| 文件大小: | 1272K |

| 代理商: | 7549 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

Rev.2.00

REJ03B0202-0200

Mar 05, 2007

Page 22 of 70

7549 Group

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

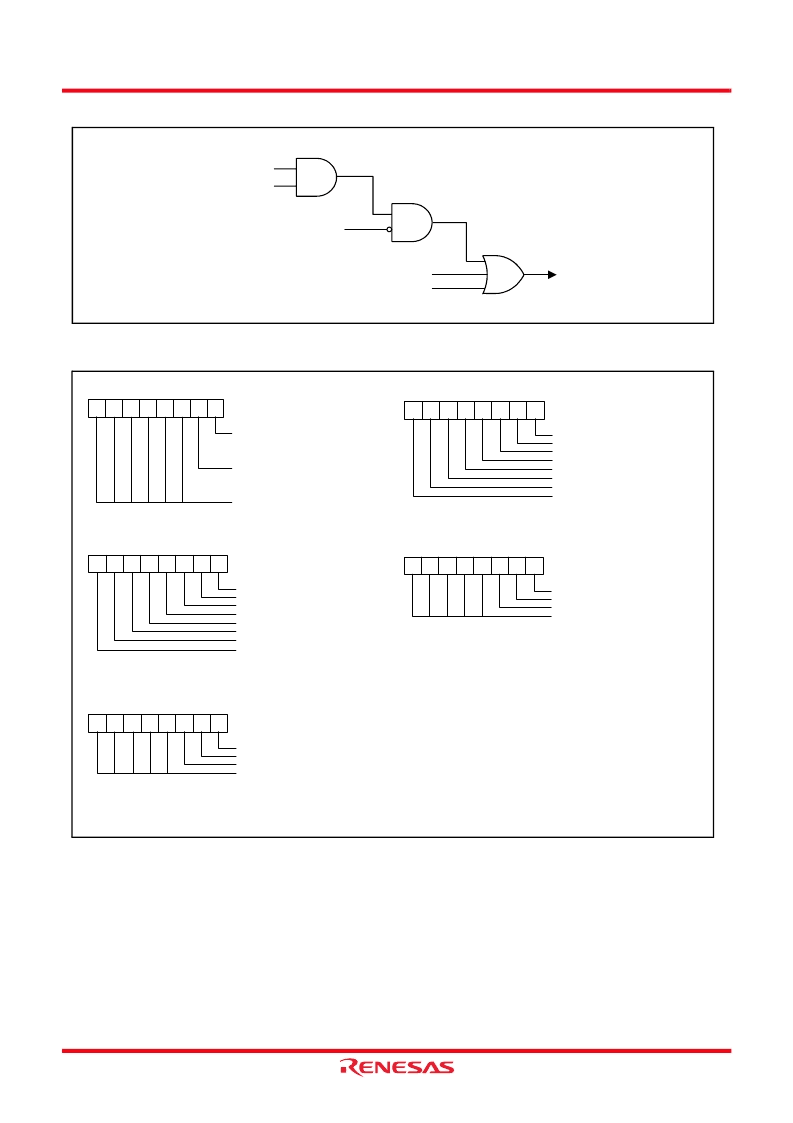

Fig 19. Interrupt control

Fig 20. Structure of Interrupt-related registers

Interrupt disable flag I

Interrupt request

Interrupt request bit

Interrupt enable bit

BRK instruction

Reset

b7

b0

INT

0

0: Falling edge active

1: Rising edge active

INT

1

0: Falling edge active

1: Rising edge active

Not used (returns “0” when read)

Interrupt edge selection register

16

, initial value: 00

16

)

b7

b0

Interrupt request register 1

16

, initial value: 00

16

)

Serial I/O receive interrupt request bit

Serial I/O transmit interrupt request bit

INT

0

interrupt request bit

INT

1

interrupt request bit

Key-on wake up interrupt request bit

Capture interrupt request bit

Compare interrupt request bit

Timer A interrupt request bit

0: No interrupt request issued

b7

b0

b7

b0

b7

b0

Interrupt request register 2

16

, initial value: 00

16

)

Timer 2 interrupt request bit

A/D conversion interrupt request bit

Timer 1 interrupt request bit

Not used (returns “0” when read)

0: No interrupt request issued

1: Interrupt request issued

Interrupt control register 1

16

, initial value: 00

16

)

Serial I/O receive interrupt enable bit

Serial I/O transmit interrupt enable bit

INT

0

interrupt enable bit

INT

1

interrupt enable bit

Key-on wake up interrupt enable bit

Capture interrupt enable bit

Compare interrupt enable bit

Timer A interrupt enable bit

0: Interrupts disabled

1: Interrupts enabled

Interrupt control register 2

16

, initial value: 00

16

)

Timer 2 interrupt enable bit

A/D conversion interrupt enable bit

Timer 1 interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit)

0: Interrupts disabled

1: Interrupts enabled

相关PDF资料 |

PDF描述 |

|---|---|

| 75HQ | SCHOTTKY RECTIFIER |

| 75HQ030 | SCHOTTKY RECTIFIER |

| 75HQ035 | SCHOTTKY RECTIFIER |

| 75HQ040 | SCHOTTKY RECTIFIER |

| 75HQ045 | SCHOTTKY RECTIFIER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 7549_0710 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 7549_09 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 7-5-4905 | 功能描述:3M 4905 VHB TAPE SPECIALTY TAPES 制造商:3m (tc) 系列:VHB?? 4905 零件状态:在售 厚度 - 粘合剂:- 厚度 - 底布,载体:- 标准包装:1 |

| 754905-1 | 功能描述:PIN ATT/ROLL AUTO IV 制造商:te connectivity amp connectors 系列:* 零件状态:有效 标准包装:1 |

| 7-5-4910 | 功能描述:3M 4910 VHB TAPE SPECIALTY TAPES 制造商:3m (tc) 系列:VHB?? 4910 零件状态:在售 底布,载体:丙烯酸泡棉 厚度 - 粘合剂:- 厚度 - 底布,载体:- 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。