- 您现在的位置:买卖IC网 > PDF目录370133 > 7549 (Renesas Technology Corp.) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF资料下载

参数资料

| 型号: | 7549 |

| 厂商: | Renesas Technology Corp. |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 单芯片8位CMOS微机 |

| 文件页数: | 39/73页 |

| 文件大小: | 1272K |

| 代理商: | 7549 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

Rev.2.00

REJ03B0202-0200

Mar 05, 2007

Page 39 of 70

7549 Group

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

Watchdog Timer

The watchdog timer gives a means for returning to a reset status

when the program fails to run on its normal loop due to a runaway.

The watchdog timer consists of an 8-bit watchdog timer H and an

8-bit watchdog timer L, being a 16-bit counter. The operation of

the watchdog timer is controlled by bits 2 to “0” in function set

ROM data 2 and the watchdog timer control register.

Watchdog timer disable bit

When the watchdog timer disable bit (bit 1 in function set ROM

data 2(FSROM2)) is set to “0”, the watchdog timer is enabled

and starts counting after reset.

Setting this bit to “1” does not operate the watchdog timer.

This bit cannot be rewritten by executing the instruction.

To use the watchdog timer, always set this bit to “0”.

After reset, the watchdog timer cannot start counting by a program.

Watchdog timer source clock selection bit

The count source of the watchdog timer is selected by the

watchdog timer source clock selection bit (bit 0 in FSROM2).

This bit cannot be rewritten by executing the instruction.

When this bit is set to “0”, the count source is always set to the

low-speed on-chip oscillator output/16.

When this bit is set to “1”, the count source is set to

φ

SOURCE/

16.

φ

SOURCE is changed by setting the clock selection bits (bits

5 and 4 in the clock mode register (CLKM: address 0037

16

)).

Watchdog timer H count source selection bit

The count source of watchdog timer H is selected by the

watchdog timer control register (WDTCON: address 0039

16

).

When the watchdog timer H count source selection bit (bit 7 in

WDTCON) is set to “0”, the count source is set to an underflow

signal from watch dog timer L. When this bit is set to “1”, the

clock selected as the count source of watchdog timer L is input to

watchdog timer H.

The initial value of this bit after releasing reset can be set by the

bit 2 in FSROM2.

Watchdog Timer Operation

Resetting or writing any data to WDTCON sets watchdog timer H

to “FF

16

” and watchdog timer L to “FF

16

”. When the watchdog

timer starts, the selected clock is counted and internal reset occurs

by the watchdog timer H underflow. Writing to WDTCON is

usually programmed to be performed before underflow.

Reading WDTCON reads the values of the high-order 6 bits in

the watchdog timer H counter and the watch dog timer count

source selection bit.

The following shows the time to watchdog timer underflow after

writing to the watchdog timer control register.

The example applies when the X

IN

input clock is selected as

φ

SOURCE and f(X

IN

) = 8 MHz.

Watchdog timer H count source selection bit = 0: 131.072 ms

Watchdog timer H count source selection bit = 1: 512

μ

s

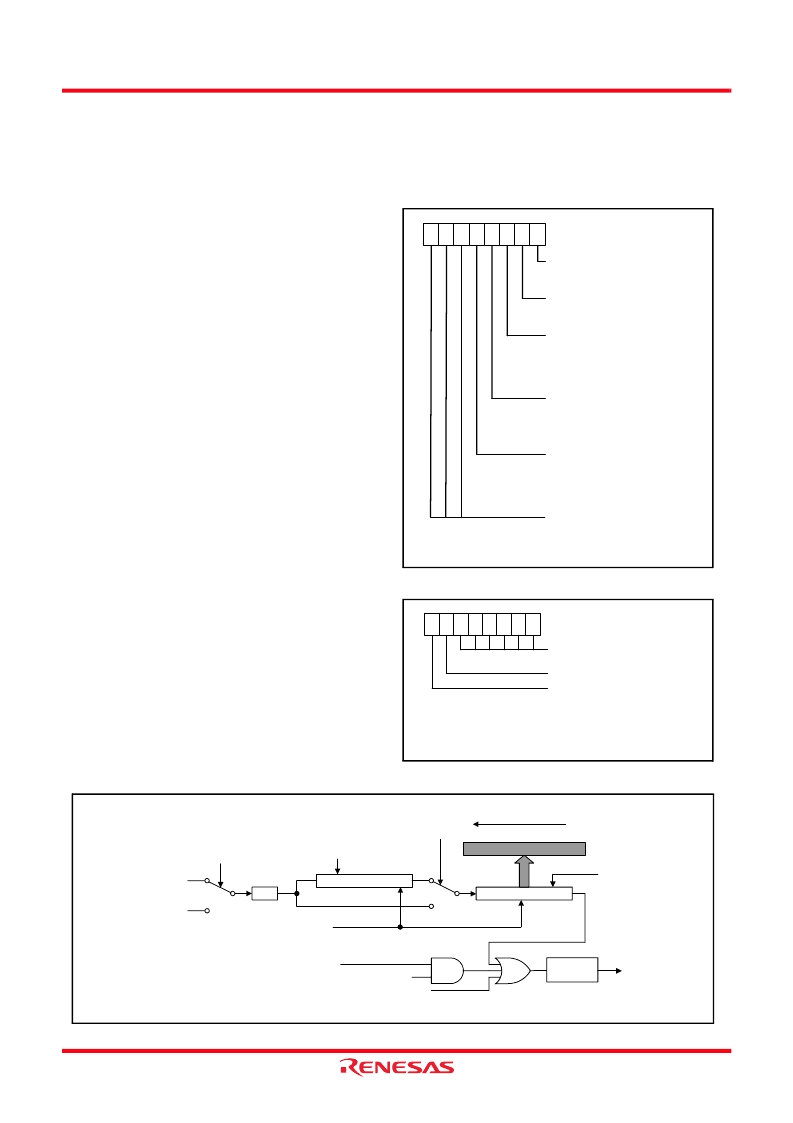

Fig 50. Structure of Function set ROM data 2

Fig 51. Structure of watchdog timer control register

Fig 52. Block diagram of watchdog timer

Watchdog timer source clock selection bit

0 : Low-speed on-chip oscillator/16

1 : System clock/16

Watchdog timer start selection bit

0 : Start watchdog timer

1 : Stop watchdog timer

Watchdog timer H count source initial value

selection bit

0 : Initial value of bit 7 of WDTCON

after reset release is “0”

1 : Initial value of bit 7 of WDTCON

after reset release is “1”

STP instruction function selection bit

0 : System enters into the stop mode

at the STP instruction execution

1 : Internal reset occurs at the STP

instruction execution

Low-speed on-chip oscillator control bit

(Note 1)

0 : Stop of low-speed on-chip oscillator

disabled

1 : Stop of low-speed on-chip oscillator

enabled

Set “0” to these bits certainly.

b7

Function set ROM data 2

FSROM2 (FFDA

16

)

b0

Note 1:

If “0” is set to this bit, it is not possible to write “1” to bit 0 in the clock

mode register. Also, the low-speed on-chip oscillator does not stop

even if the STP instruction is executed.

Watchdog timer H (read only for

high-order 6-bit)

Not used (returns “0” when read)

Watchdog timer H count source

selection bit

0 : Watchdog timer L underflow

1 : Low-speed on-chip oscillator/16

or

φ

SOURCE/16

Watchdog timer control register (Note)

(WDTCON: address 0039

16

,

initial value: X0111111

2

)

b7

b0

Note:

The initial value of this register is changes by setting of

function set ROM data 2.

Watchdog timer H (8)

Data bus

Watchdog timer L (8)

“FF

16

” is set at

WDTCON writing

1/16

φ

SOURCE

Low-speed on-chip

oscillator

Watchdog timer source

clock selection bit

(bit 0 of FSROM2)

Watchdog timer start

selection bit

(bit 1 of FSROM2)

Reset

circuit

Internal reset

STP instruction function

selection bit

(bit 3 of FSROM2)

STP Instruction

Reset pin input

Watchdog timer H

count source selection bit

(bit 7 of WDTCON)

Watchdog timer H count source

initial value selection bit

(bit 2 of FSROM2)

FSROM2: Function set ROM data 2

WDTCON: Watchdog timer control register

CPUM: CPU mode register

“FF

16

” is set at

WDTCON writing

Initial value setting

after releasing reset

相关PDF资料 |

PDF描述 |

|---|---|

| 75HQ | SCHOTTKY RECTIFIER |

| 75HQ030 | SCHOTTKY RECTIFIER |

| 75HQ035 | SCHOTTKY RECTIFIER |

| 75HQ040 | SCHOTTKY RECTIFIER |

| 75HQ045 | SCHOTTKY RECTIFIER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 7549_0710 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 7549_09 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 7-5-4905 | 功能描述:3M 4905 VHB TAPE SPECIALTY TAPES 制造商:3m (tc) 系列:VHB?? 4905 零件状态:在售 厚度 - 粘合剂:- 厚度 - 底布,载体:- 标准包装:1 |

| 754905-1 | 功能描述:PIN ATT/ROLL AUTO IV 制造商:te connectivity amp connectors 系列:* 零件状态:有效 标准包装:1 |

| 7-5-4910 | 功能描述:3M 4910 VHB TAPE SPECIALTY TAPES 制造商:3m (tc) 系列:VHB?? 4910 零件状态:在售 底布,载体:丙烯酸泡棉 厚度 - 粘合剂:- 厚度 - 底布,载体:- 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。