参数资料

| 型号: | AD9974BBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/52页 |

| 文件大小: | 0K |

| 描述: | IC CCDSP DUAL 14BIT 100-CSPBGA |

| 标准包装: | 1 |

| 类型: | CCD 信号处理器,14 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 电流 - 电源: | 55mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LFBGA,CSPBGA |

| 供应商设备封装: | 100-CSBGA(9x9) |

| 包装: | 标准包装 |

| 其它名称: | AD9974BBCZRLDKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9974

Rev. A | Page 19 of 52

Table 11. CLPOB and PBLK Pattern Registers

Parameter

Length (Bits)

Range

Description

CLPOB0_TOG1

13

0 to 8191 pixel location

First CLPOB0 toggle position within the line for each V-sequence.

CLPOB0_TOG2

13

0 to 8191 pixel location

Second CLPOB0 toggle position within the line for each V-sequence.

CLPOB1_TOG1

13

0 to 8191 pixel location

First CLPOB1 toggle position within the line for each V-sequence.

CLPOB1_TOG2

13

0 to 8191 pixel location

Second CLPOB1 toggle position within the line for each V-sequence.

CLPOB_POL

9

High/low

Starting polarity of CLPOB for each V-sequence [8:0] (in field registers).

CLPOB_PAT

9

0 to 9 settings

CLPOB pattern selection for each V-sequence [8:0] (in field registers).

CLPOBMASKSTART

13

0 to 8191 pixel location

CLPOB mask start position: three values available (in field registers).

CLPOBMASKEND

13

0 to 8191 pixel location

CLPOB mask end position: three values available (in field registers).

PBLK0_TOG1

13

0 to 8191 pixel location

First PBLK0 toggle position within the line for each V-sequence.

PBLK0_TOG2

13

0 to 8191 pixel location

Second PBLK0 toggle position within the line for each V-sequence.

PBLK1_TOG1

13

0 to 8191 pixel location

First PBLK1 toggle position within the line for each V-sequence.

PBLK1_TOG2

13

0 to 8191 pixel location

Second toggle position within the line for each V-sequence.

PBLK_POL

9

High/low

Starting polarity of PBLK for each V-sequence [8:0] (in field registers).

PBLK_PAT

9

0 to 9 settings

PBLK pattern selection for each V-sequence [8:0] (in field registers).

PBLKMASKSTART

13

0 to 8191 pixel location

PBLK mask start position: three values available (in field registers).

PBLKMASKEND

13

0 to 8191 pixel location

PBLK mask end position: three values available (in field registers).

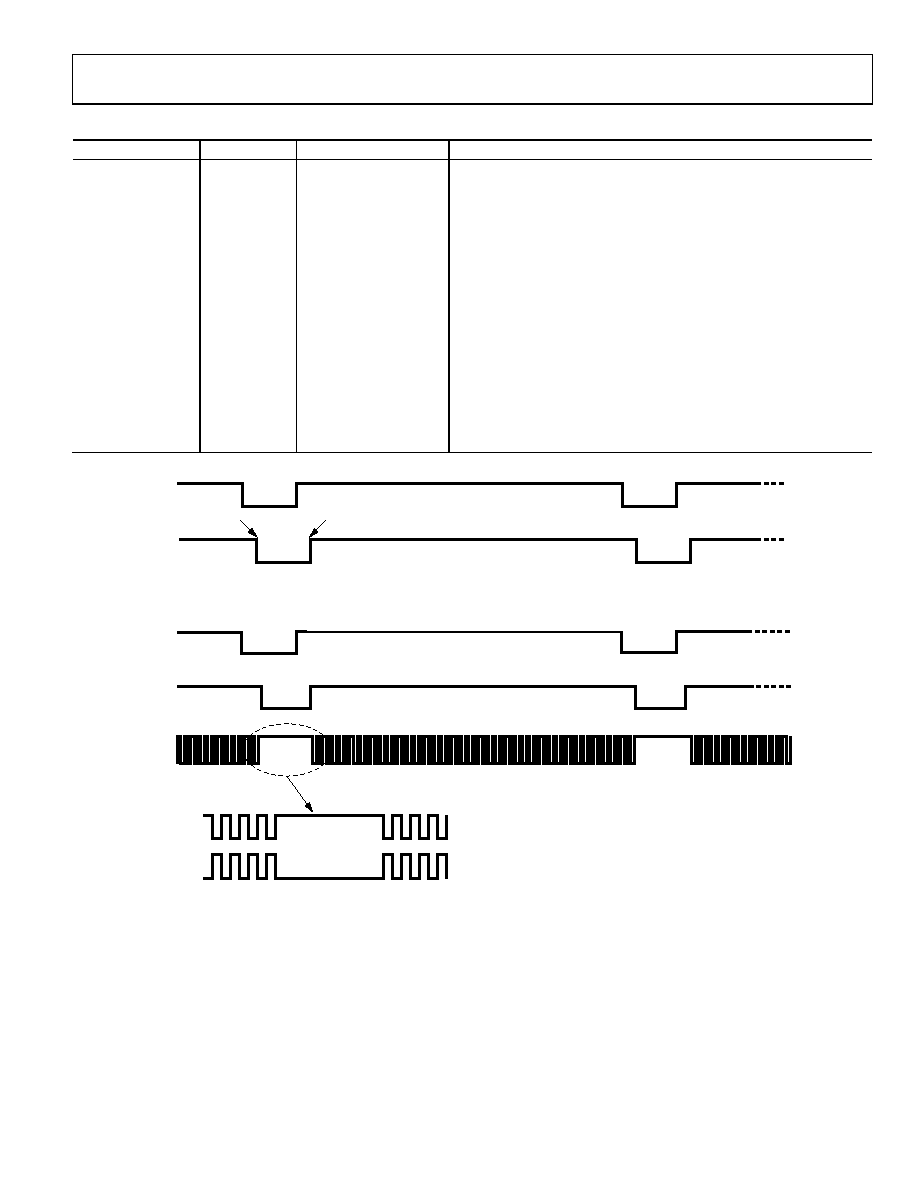

HD

HBLK

BASIC HBLK PULSE IS GENERATED USING HBLKTOGE1 AND HBLKTOGE2 REGISTERS (HBLKALT = 0).

BLANK

HBLKTOGE1

HBLKTOGE2

05

95

5-

0

25

Figure 25. Typical Horizontal Blanking Pulse Placement (HBLKMODE = 0)

HD

HBLK

H1/H3

H2/H4

THE POLARITY OF H1/H3 DURING BLANKING IS PROGRAMMABLE

(H2/H4 POLARITY IS SEPARATELY PROGRAMMABLE)

05

95

5-

02

6

Figure 26. HBLK Masking Control

相关PDF资料 |

PDF描述 |

|---|---|

| AD9979BCPZRL | IC PROCESSOR CCD 14BIT 48-LFCSP |

| AD9980KSTZ-95 | IC INTERFACE 8BIT ANALOG 80LQFP |

| AD9981KSTZ-95 | IC INTERFACE 10BIT ANALOG 80LQFP |

| AD9983AKSTZ-170 | IC DISPLAY 8BIT 170MSPS 80LQFP |

| AD9985KSTZ-140 | IC INTERFACE 8BIT 140MSPS 80LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9975 | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABST | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTEB | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTRL | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:10 BIT ANALOG FRONT END WITH HALF DUPLEX - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。