参数资料

| 型号: | AD9974BBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 15/52页 |

| 文件大小: | 0K |

| 描述: | IC CCDSP DUAL 14BIT 100-CSPBGA |

| 标准包装: | 1 |

| 类型: | CCD 信号处理器,14 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 电流 - 电源: | 55mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LFBGA,CSPBGA |

| 供应商设备封装: | 100-CSBGA(9x9) |

| 包装: | 标准包装 |

| 其它名称: | AD9974BBCZRLDKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9974

Rev. A | Page 22 of 52

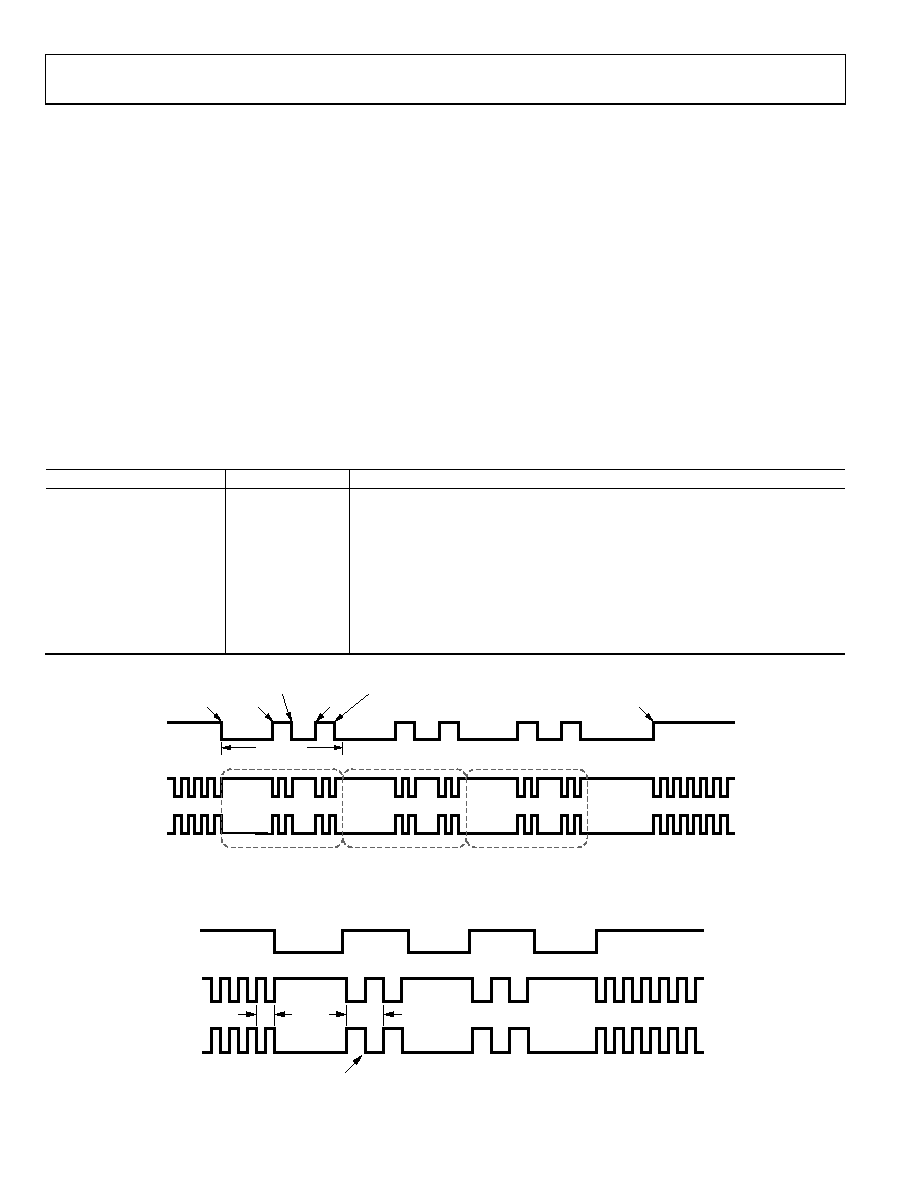

HBLK Mode 1 Operation

Enable multiple repeats of the HBLK signal by setting

HBLK_MODE to 1. In this mode, the HBLK pattern can be

generated using a different set of registers: HBLKSTART,

HBLKEND, HBLKLEN, and HBLKREP, along with the six

toggle positions (see Figure 28).

Separate toggle positions are available for even and odd lines.

If alternation is not needed, load the same values into the registers

for even (HBLKTOGE) and odd (HBLKTOGO) lines.

Generating HBLK Line Alternation

HBLK Mode 0 and HBLK Mode 1 provide the ability to

alternate different HBLK toggle positions on even and odd

lines. Separate toggle positions are available for even and odd

lines. If even/odd line alternation is not required, load the same

values into the registers for even (HBLKTOGE) and odd

(HBLKTOGO) lines.

Increasing H-Clock Width During HBLK

HBLK Mode 0 and HBLK Mode 1 allow the H1 to H4 pulse

width to be increased during the HBLK interval. As shown in

Figure 29, the H-clock frequency can be reduced by a factor of

1/2, 1/4, 1/6, 1/8, 1/10, 1/12, and so on, up to 1/30. To enable this

feature, the HCLK_WIDTH register (Address 0x34[7:4]) is set to

a value between 1 and 15. When this register is set to 0, the wide

HCLK feature is disabled. The reduced frequency occurs only for

H1 to H4 pulses that are located within the HBLK area.

The HCLK_WIDTH register is generally used in conjunction

with special HBLK patterns to generate vertical and horizontal

mixing in the CCD.

Note that the wide HCLK feature is available only in HBLK Mode 0

and HBLK Mode 1, not in HBLK Mode 2.

Table 13. HCLK Width Register

Register

Length (Bits)

Description

HCLK_WIDTH

4

Controls H1 to H4 width during HBLK as a fraction of pixel rate.

0 = same frequency as pixel rate.

1 = 1/2 pixel frequency, that is, doubles the HCLK pulse width.

2 = 1/4 pixel frequency.

3 = 1/6 pixel frequency.

4 = 1/8 pixel frequency.

5 = 1/10 pixel frequency.

…

15 = 1/30 pixel frequency.

HBLK

H-BLANK REPEATING PATTERN IS CREATED USING HBLKLEN AND HBLKREP REGISTERS.

H1/H3

H2/H4

HBLKSTART HBLKTOGE1

HBLKTOGE2

HBLKEND

HBLKTOGE3

HBLKTOGE4

HBLKLEN

HBLKREP NUMBER 1

HBLKREP NUMBER 2

HBLKREP NUMBER 3

HBLKREP = 3

05

95

5-

02

8

Figure 28. HBLK Repeating Pattern Using HBLKMODE = 1

HBLK

H-CLOCK FREQUENCY CAN BE REDUCED DURING HBLK BY 1/2 (AS SHOWN),

1/4, 1/6, 1/8, 1/10, 1/12, AND SO ON, UP TO 1/30 USING HBLKWIDTH REGISTER.

H1/H3

H2/H4

1/FPIX

2 × (1/FPIX)

0

59

55

-02

9

Figure 29. Generating Wide H-Clock Pulses During HBLK Interval

相关PDF资料 |

PDF描述 |

|---|---|

| AD9979BCPZRL | IC PROCESSOR CCD 14BIT 48-LFCSP |

| AD9980KSTZ-95 | IC INTERFACE 8BIT ANALOG 80LQFP |

| AD9981KSTZ-95 | IC INTERFACE 10BIT ANALOG 80LQFP |

| AD9983AKSTZ-170 | IC DISPLAY 8BIT 170MSPS 80LQFP |

| AD9985KSTZ-140 | IC INTERFACE 8BIT 140MSPS 80LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9975 | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABST | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTEB | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTRL | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:10 BIT ANALOG FRONT END WITH HALF DUPLEX - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。