参数资料

| 型号: | AD9974BBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/52页 |

| 文件大小: | 0K |

| 描述: | IC CCDSP DUAL 14BIT 100-CSPBGA |

| 标准包装: | 1 |

| 类型: | CCD 信号处理器,14 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 电流 - 电源: | 55mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LFBGA,CSPBGA |

| 供应商设备封装: | 100-CSBGA(9x9) |

| 包装: | 标准包装 |

| 其它名称: | AD9974BBCZRLDKR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9974

Rev. A | Page 36 of 52

STANDBY MODE OPERATION

The AD9974 contains two standby modes to optimize the

overall power dissipation in a particular application. Bit 1 and

Bit 0 of Address 0x00 control the power-down state of the device.

STANDBY[1:0] = 00 = normal operation (full power)

STANDBY[1:0] = 01 = reference standby mode

STANDBY[1:0] = 10 or 11 = total shutdown mode

(lowest power)

Table 20 summarizes the operation of each power-down mode.

The OUT_CONTROL register takes priority over the reference

standby mode in determining the digital output states, but total

shutdown mode takes priority over OUT_CONTROL. Total

shutdown mode has the lowest power consumption.

When returning from total shutdown mode to normal operation,

the timing core must be reset at least 100 μs after the STANDBY

register is written to.

There is an additional register to disable the internal voltage

reference buffer (Address 0x00[2]) independently. By default

the buffer is disabled, but it must be enabled for normal operation.

CLI FREQUENCY CHANGE

If the input clock, CLI, is interrupted or changes to a different

frequency, the timing core must be reset for proper operation.

After the CLI clock has settled to the new frequency, or the

previous frequency has resumed, write 0 and then 1 to the

TGCORE_RST register (Address 0x14). This guarantees proper

timing core operation.

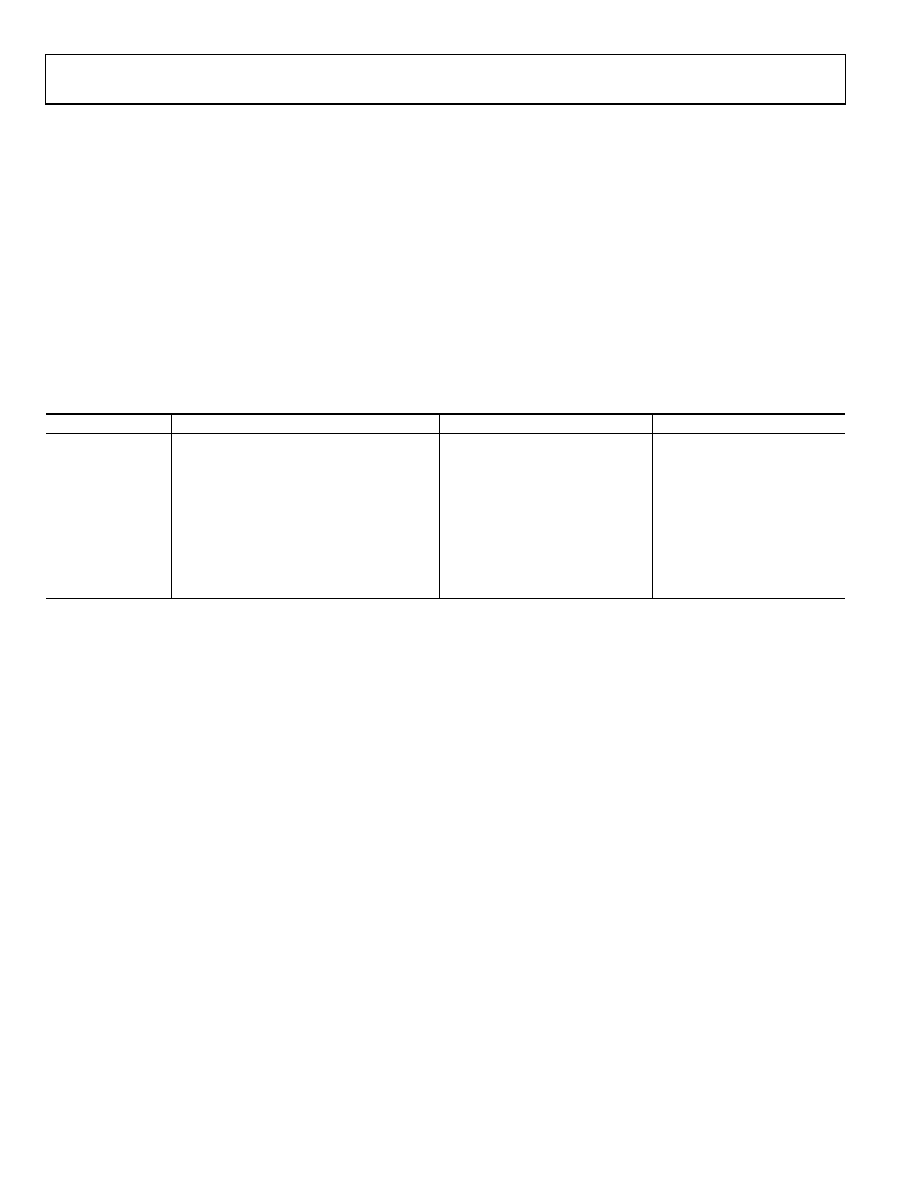

Table 20. Standby Mode Operation

I/O Block

Total Shutdown (Default)1, 2

OUT_CONTROL = Low2

Reference Standby

AFE

Off

No change

Only REFT, REFB on

Timing Core

Off

No change

On

H1

High-Z

Low

Low (4.3 mA)

H2

High-Z

High

High (4.3 mA)

H3

High-Z

Low

Low (4.3 mA)

H4

High-Z

High

High (4.3 mA)

HL

High-Z

Low

Low (4.3 mA)

RG

High-Z

Low

Low (4.3 mA)

DOUT

Low3

Low

1 To exit total shutdown, write 00 to STANDBY (Address 0x00, Bits[1:0]), then reset the timing core after 100 μs to guarantee proper settling.

2 Total shutdown mode takes priority over OUT_CONTROL for determining the output polarities.

3 The status of the DOUT pins is unknown at power-up. Low status is guaranteed in total shutdown mode after the power-up sequence is completed.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9979BCPZRL | IC PROCESSOR CCD 14BIT 48-LFCSP |

| AD9980KSTZ-95 | IC INTERFACE 8BIT ANALOG 80LQFP |

| AD9981KSTZ-95 | IC INTERFACE 10BIT ANALOG 80LQFP |

| AD9983AKSTZ-170 | IC DISPLAY 8BIT 170MSPS 80LQFP |

| AD9985KSTZ-140 | IC INTERFACE 8BIT 140MSPS 80LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9975 | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABST | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTEB | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTRL | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:10 BIT ANALOG FRONT END WITH HALF DUPLEX - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。