参数资料

| 型号: | AD9974BBCZRL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/52页 |

| 文件大小: | 0K |

| 描述: | IC CCDSP DUAL 14BIT 100-CSPBGA |

| 标准包装: | 1 |

| 类型: | CCD 信号处理器,14 位 |

| 输入类型: | 逻辑 |

| 输出类型: | 逻辑 |

| 接口: | 3 线串口 |

| 电流 - 电源: | 55mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LFBGA,CSPBGA |

| 供应商设备封装: | 100-CSBGA(9x9) |

| 包装: | 标准包装 |

| 其它名称: | AD9974BBCZRLDKR |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

AD9974

Rev. A | Page 13 of 52

TERMINOLOGY

Differential Nonlinearity (DNL)

An ideal ADC exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Therefore,

every code must have a finite width. No missing codes guaranteed

to 14-bit resolution indicates that all 16,384 codes, each for its

respective input, must be present over all operating conditions.

Peak Nonlinearity

Peak nonlinearity, a full signal chain specification, refers to the

peak deviation of the output of the AD9974 from a true straight

line. The point used as zero scale occurs 0.5 LSB before the first

code transition. Positive full scale is defined as a level 1 LSB

and 0.5 LSB beyond the last code transition. The deviation is

measured from the middle of each particular output code to the

true straight line. The error is then expressed as a percentage

of the 2 V ADC full-scale signal. The input signal is always

appropriately gained up to fill the ADC full-scale range.

Total Output Noise

The rms output noise is measured using histogram techniques.

The standard deviation of the ADC output codes is calculated

in LSB and represents the rms noise level of the total signal

chain at the specified gain setting. The output noise can be

converted to an equivalent voltage using the relationship

1 LSB = (ADC Full Scale/2n Codes)

where n is the bit resolution of the ADC. For the AD9974,

1 LSB is approximately 122.0 μV.

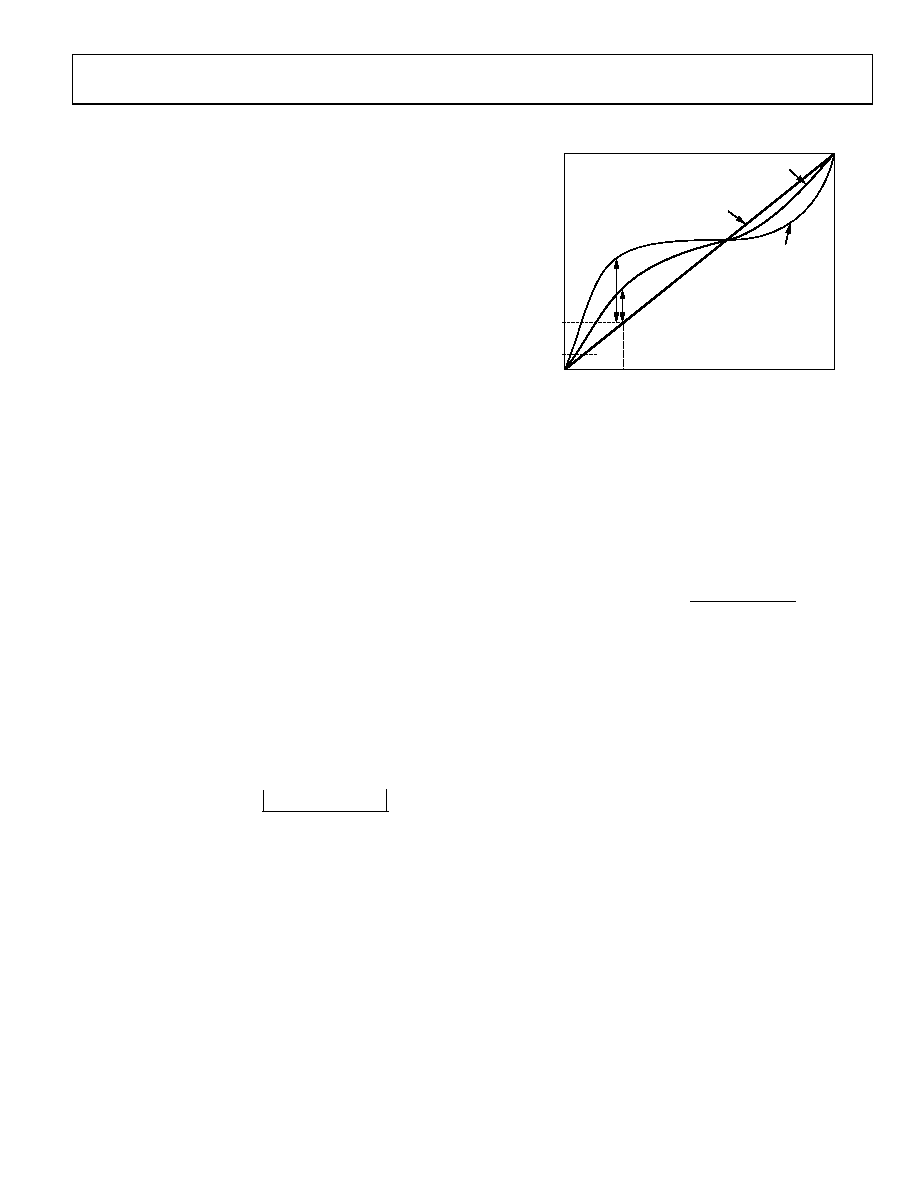

Linearity Mismatch

The linearity mismatch is calculated by taking the difference in

INL of the two channels at Input X, and then expressing the

difference as a percentage of the output code at X. The values

given in Table 2 are obtained over the range of 116 and

maximum of the output code. The general trend is for the

linearity mismatch to decrease as the output approaches the

maximum code, as shown in Figure 8.

)

(

)

(

)

(

(%)

X

Code

Output

X

B

INL

X

A

INL

Mismatch

Linearity

=

CHANNEL B

INPUT VOLTAGE

OU

TP

U

T

C

O

D

E

(L

S

B

)

XFS

INL A(X)

INL B(X)

OUTPUT (X)

MAX/16

0

MAX

CHANNEL A

IDEAL

0

59

55

-00

4

Figure 13. Linearity Mismatch Definition

Power Supply Rejection (PSR)

The PSR is measured with a step change applied to the supply

pins. The PSR specification is calculated from the change in the

data outputs for a given step change in the supply voltage.

Crosstalk

The crosstalk is measured while applying a full-scale step to

one channel and measuring the interference on the opposite

channel.

×

=

384

,

16

)

(

log

20

)

dB

(

LSB

ce

Interferen

Crosstalk

相关PDF资料 |

PDF描述 |

|---|---|

| AD9979BCPZRL | IC PROCESSOR CCD 14BIT 48-LFCSP |

| AD9980KSTZ-95 | IC INTERFACE 8BIT ANALOG 80LQFP |

| AD9981KSTZ-95 | IC INTERFACE 10BIT ANALOG 80LQFP |

| AD9983AKSTZ-170 | IC DISPLAY 8BIT 170MSPS 80LQFP |

| AD9985KSTZ-140 | IC INTERFACE 8BIT 140MSPS 80LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9975 | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABST | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTEB | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975ABSTRL | 制造商:AD 制造商全称:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9975BST | 制造商:Analog Devices 功能描述:Mixed Signal Front End 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:10 BIT ANALOG FRONT END WITH HALF DUPLEX - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。