- 您现在的位置:买卖IC网 > PDF目录2063 > ADAU1445YSVZ-3A-RL (Analog Devices Inc)IC SIGMADSP 175MHZ 100TQFP PDF资料下载

参数资料

| 型号: | ADAU1445YSVZ-3A-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/92页 |

| 文件大小: | 0K |

| 描述: | IC SIGMADSP 175MHZ 100TQFP |

| 标准包装: | 1,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 车载音频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP 裸露焊盘 |

| 供应商设备封装: | 100-TQFP-EP(14x14) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADAU1445/ADAU1446

Rev. A | Page 19 of 92

MASTER CLOCK AND PLL

Using the Oscillator

The ADAU1445/ADAU1446 can use an on-board oscillator to

generate its master clock. However, an external crystal must be

attached to complete the oscillator circuit. The on-board oscillator

is designed to work with a 256 × fS,NORMAL master clock, which is

12.288 MHz when fS,NORMAL is 48 kHz and 11.2896 MHz when

fS,NORMAL is 44.1 kHz. The resonant frequency of this crystal should

be in this range even in the case when the core is processing

dual- or quad-rate signals. When the core is processing dual-

rate signals (for example, fS,DUAL = 88.2 kHz or 96 kHz), resonant

frequency of the crystal should be 128 × fS,DUAL; when the core is

processing quad-rate signals (for example, fS,QUAD = 192 kHz),

the resonant frequency of the crystal should be 64 × fS,QUAD.

The external crystal in the circuit should be an AT-cut parallel

resonance device operating at its fundamental frequency.

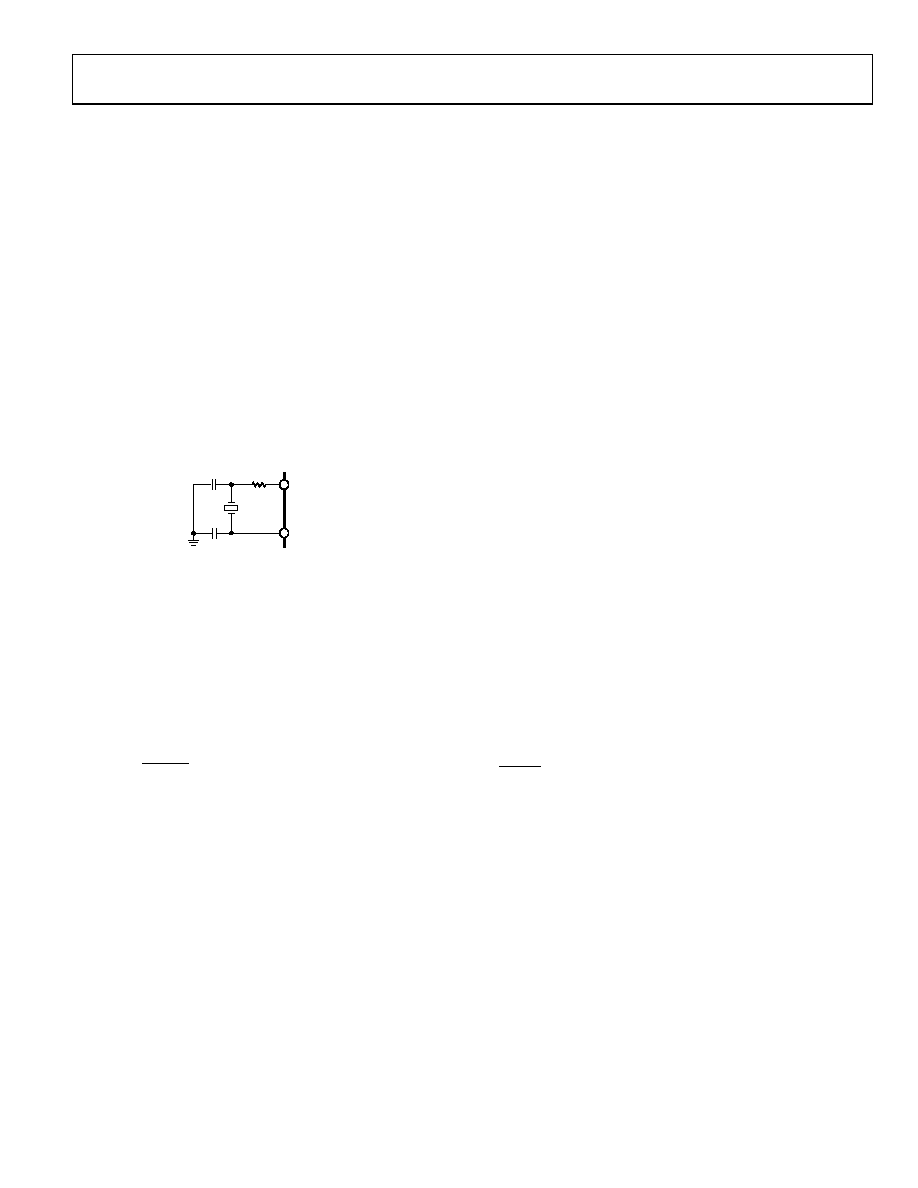

Ceramic resonators should not be used. Figure 9 shows the

crystal oscillator circuit recommended for proper operation.

C1

100

XTALO

C2

XTALI

07

69

6-

0

09

Figure 9. Crystal Oscillator Circuit

The 100 Ω damping resistor on XTALO provides the oscillator

with a voltage swing of approximately 2.2 V at the XTALI pin.

The crystal shunt capacitance should be 7 pF. Its optimal load

capacitance, specified by the manufacturer, should be about 18 pF,

although the circuit supports values up to 25 pF. The equivalent

series resistance should also be as small as possible. The necessary

values of Load Capacitor C1 and Load Capacitor C2 can be

calculated from the crystal load capacitance with the following

equation:

STRAY

2

1

2

1

L

C

+

×

=

where CSTRAY is the stray capacitance in the circuit and is usually

assumed to be approximately 2 pF to 5 pF.

Short trace lengths in the oscillator circuit decrease stray

capacitance, thereby increasing the loop gain of the circuit and

helping to avoid crystal start-up problems.

On the ADAU1445/ADAU1446 evaluation boards, the capac-

itance value for C1 and C2 is 22 pF.

XTALO should not be used to directly drive the crystal signal to

another IC. This signal is an analog sine wave and is not appro-

priate to drive a digital input. A separate pin, CLKOUT, is provided

for this purpose. CLKOUT can output 256 × fS,NORMAL, 512 ×

fS,NORMAL, or a buffered, digital copy of the crystal oscillator

signal to other ICs in the system. CLKOUT is set up using the

CLKMODEx pins. For a more detailed explanation of CLKOUT,

refer to the Using the ADAU1445/ADAU1446 as Clock Master

section.

Setting Master Clock and PLL Mode

The ADAU1445/ADAU1446 master clock input feeds a PLL, which

generates the 3584 × fS,NORMAL clock (172.032 MHz when fS,NORMAL

is 48 kHz) to run the DSP core. This rate is referred to as fCORE.

In normal operation, the input to the master clock must be one

of the following: 64 × fS,NORMAL, 128 × fS,NORMAL, 256 × fS,NORMAL,

384 × fS,NORMAL, or 512 × fS,NORMAL, where fS,NORMAL is the audio

sampling rate with the core in normal-rate processing mode.

The PLL divider mode is set by PLL0, PLL1, and PLL2 as

detailed in Table 7.

If the ADAU1445/ADAU1446 cores are set to receive dual-rate

signals (by reducing the number of program steps per sample by

a factor of 2 using the DSP core rate select register), then the master

clock frequency must be 32 × fS,DUAL, 64 × fS,DUAL, 128 × fS,DUAL,

192 × fS,DUAL, or 256 × fS,DUAL.

If the ADAU1445/ADAU1446 cores are set to receive quad-rate

signals (by reducing the number of program steps per sample by

a factor of 4 using the DSP core rate select register), then the master

clock frequency must be 16 × fS,QUAD, 32 × fS,QUAD, 64 × fS,QUAD,

96 × fS,QUAD, or 128 × fS,QUAD. On power-up, a clock signal must

be present on XTALI so that the ADAU1445/ADAU1446 can

complete its initialization routine.

If, at any point during operation, the clock signal is removed

from XTALI, the DSP should be reset to avoid unpredictable

behavior on output pins. The clock mode should not be changed

without also resetting the ADAU1445/ADAU1446. If the mode

is changed during operation, a click or pop can result on the

outputs. The state of the PLLx pins should be changed while

RESET is held low.

The phase-locked loop uses the PLL mode select pins (PLL0,

PLL1, and PLL2) to derive a 64 × fS,NORMAL clock from whatever

signal is present at the XTALI pin. This clock signal is multiplied

by 56 to produce the core clock. Therefore, fCORE is 3584 × fS,NORMAL.

In a system with a fS,NORMAL of 48 kHz, the PLL derives a 3.072 MHz

clock and then multiplies it by 56 to produce a 172.032 MHz

core clock.

The core clock (fCORE) should never exceed 172.032 MHz,

though it may be lower in some applications.

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1461WBCPZ-R7 | IC SIGMADSP 24BIT 96KHZ PLL 32 |

| ADAU1513ACPZ-RL7 | IC AMP AUDIO PWR 23W 48LFCSP |

| ADAU1590ACPZ-RL7 | IC AMP AUDIO PWR 48LFCSP |

| ADAU1592ACPZ | IC AMP AUDIO PWR 24W 48LFCSP |

| ADAU1701JSTZ-RL | IC AUDIO PROC 2ADC/4DAC 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1446EBZ | 制造商:Analog Devices 功能描述:SIGMADSP? DIGITAL AUDIO PROCESSOR WITH FLEXIBLE AUDIO - Bulk |

| ADAU1446YSTZ-3A | 功能描述:IC SIGMADSP 175MHZ 100LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1446YSTZ-3A-RL | 功能描述:IC SIGMADSP 175MHZ 100LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1450WBCPZ | 功能描述:IC AUDIO PROCESSOR 72LFCSP 制造商:analog devices inc. 系列:SigmaDSP? 包装:托盘 零件状态:有效 类型:Sigma 接口:I2C,SPI 时钟速率:147.456MHz 非易失性存储器:- 片载 RAM:64KB 电压 - I/O:3.3V 电压 - 内核:1.20V 工作温度:-40°C ~ 105°C(TA) 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP-VQ(10x10) 标准包装:1 |

| ADAU1450WBCPZ-RL | 功能描述:IC AUDIO PROCESSOR 72LFCSP 制造商:analog devices inc. 系列:SigmaDSP? 包装:剪切带(CT) 零件状态:在售 类型:Sigma 接口:I2C,SPI 时钟速率:147.456MHz 非易失性存储器:- 片载 RAM:64KB 电压 - I/O:3.30V 电压 - 内核:1.20V 工作温度:-40°C ~ 105°C(TA) 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP-VQ(10x10) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。