- 您现在的位置:买卖IC网 > PDF目录2063 > ADAU1445YSVZ-3A-RL (Analog Devices Inc)IC SIGMADSP 175MHZ 100TQFP PDF资料下载

参数资料

| 型号: | ADAU1445YSVZ-3A-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 26/92页 |

| 文件大小: | 0K |

| 描述: | IC SIGMADSP 175MHZ 100TQFP |

| 标准包装: | 1,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 车载音频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP 裸露焊盘 |

| 供应商设备封装: | 100-TQFP-EP(14x14) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADAU1445/ADAU1446

Rev. A | Page 32 of 92

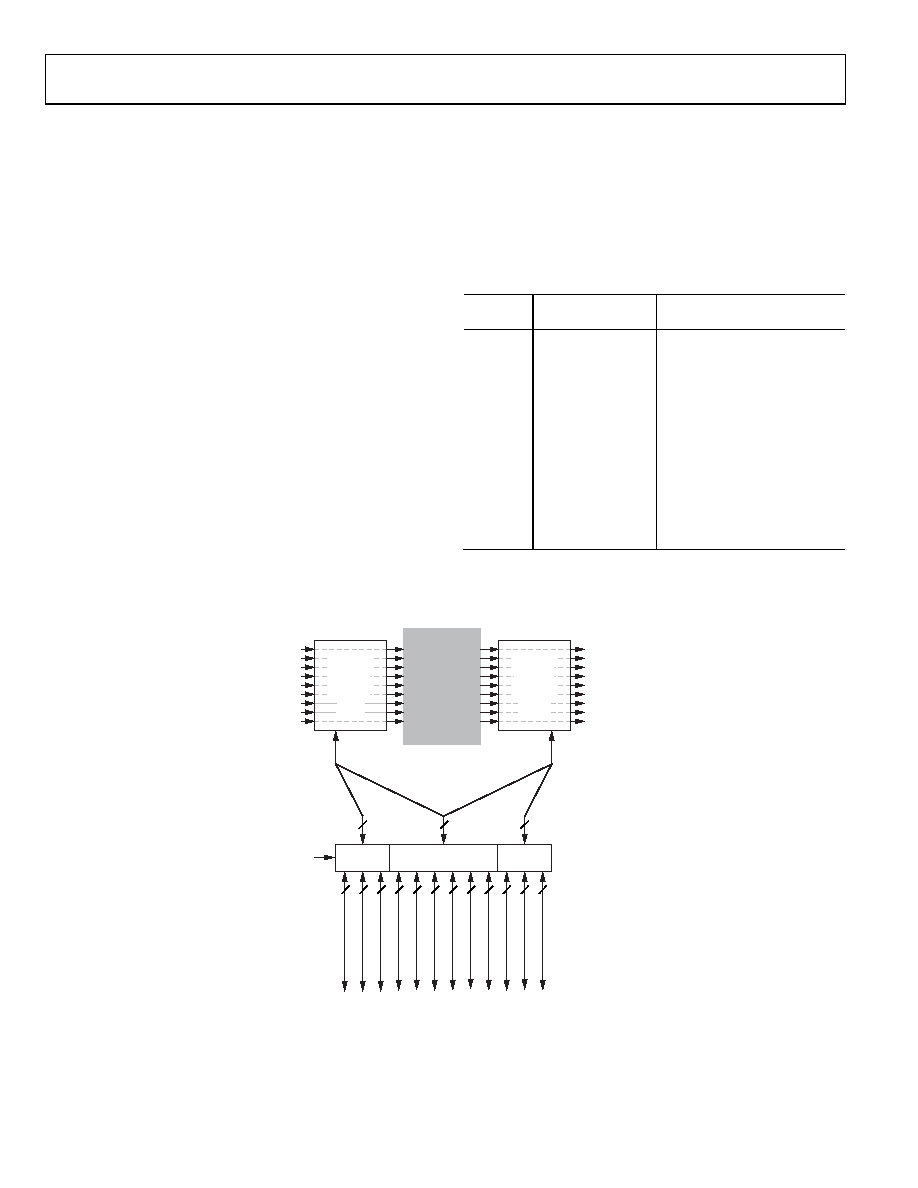

Serial Clock Domains

There are 12 clock domains (pairs of LRCLKx and BCLKx pins)

available in the ADAU1445/ADAU1446. Of these, three are avail-

able exclusively to the serial data input ports, three are available

exclusively to the serial data output ports, and the remaining six

can be assigned to clock either input or output ports.

The ADAU1445 contains two 8-channel ASRCs, whereas the

ADAU1446 contains no ASRCs. However, all clock domain pins

are available on every IC in the ADAU1445/ADAU1446. In a

system with no sample rate conversion and with serial ports in

slave mode, at least two pairs of LRCLKx and BCLKx pins must

be connected: one pair for the input serial ports and one pair

for the output serial ports. If all serial ports are in master mode

and synchronous, then only one pair of LRCLKx and BCLKx pins

needs to be connected.

Figure 27 shows a simplified view of the assignment of clock

domains to the input and output sides of the chip. Note that

each clock domain comprises two signals, namely the BCLK

(bit clock) and LRCLK (frame clock). Therefore, the 12 clock

domains contain a total of 24 clock signals.

Each clock domain is capable of acting as a master or slave. For

this reason, all LRCLK and BCLK pins are bidirectional. In slave

mode, the LRCLK and BCLK pins receive clock signals from an

external source, such as a codec. In master mode, the LRCLK

and BCLK pins output clock signals to external slave ICs.

Although a clock domain in slave mode can clock an arbitrary

number of serial ports, a clock domain in master mode can only

clock a single serial port. For Clock Domains[2:0] and Clock

Domains[11:9], the corresponding serial port is fixed as an input

or output. For assignable clock domains (Clock Domains[8:3]),

the corresponding serial port can be either an input or output,

depending on the setting of the clock pad multiplexer register

(see Table 18 for more details).

Table 18. Master Mode Clock Domain Assignment

Clock

Domain

Chip Pins

Serial Port

0

LRCLK0, BCLK0

SDATA_IN0

1

LRCLK1, BCLK1

SDATA_IN1

2

LRCLK2, BCLK2

SDATA_IN2

3

LRCLK3, BCLK3

SDATA_IN3 or SDATA_OUT31

4

LRCLK4, BCLK4

SDATA_IN4 or SDATA_OUT41

5

LRCLK5, BCLK5

SDATA_IN5 or SDATA_OUT51

6

LRCLK6, BCLK6

SDATA_IN6 or SDATA_OUT61

7

LRCLK7, BCLK7

SDATA_IN7 or SDATA_OUT71

8

LRCLK8, BCLK8

SDATA_IN8 or SDATA_OUT81

9

LRCLK9, BCLK9

SDATA_OUT0

10

LRCLK10, BCLK10

SDATA_OUT1

11

LRCLK11, BCLK11

SDATA_OUT2

1 Depends on the setting of the clock pad multiplexer register (Address 0xE240).

SERIAL

INPUT

PORTS

(×9)

SERIAL

OUTPUT

PORTS

(×9)

CLOCK DOMAINS

(×12)

0 TO 2

3 TO 8

9 TO 11

MASTER/SLAVE

SELECT

SDATA_IN0

SDATA_IN1

SDATA_IN2

SDATA_IN3

SDATA_IN4

SDATA_IN5

SDATA_IN6

SDATA_IN7

SDATA_IN8

SDATA_OUT0

SDATA_OUT1

SDATA_OUT2

SDATA_OUT3

SDATA_OUT4

SDATA_OUT5

SDATA_OUT6

SDATA_OUT7

SDATA_OUT8

BCL

K0/

L

R

C

L

K

0

BC

L

K

1/

L

R

CL

K1

BC

L

K

2/

L

R

CL

K2

BC

L

K

3/

L

R

CL

K3

BC

L

K

4/

L

R

CL

K4

BC

L

K

5/

L

R

CL

K5

BC

L

K

6/

L

R

CL

K6

BC

L

K

7/

L

R

CL

K7

BC

L

K

8/

L

R

CL

K8

BC

L

K

9/

L

R

CL

K9

BCL

K10

/L

RCL

K10

BCL

K11

/L

RCL

K11

2

6

12

6

2

07

69

6-

0

26

Figure 27. Simplified Serial Clock Domain Assignment

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1461WBCPZ-R7 | IC SIGMADSP 24BIT 96KHZ PLL 32 |

| ADAU1513ACPZ-RL7 | IC AMP AUDIO PWR 23W 48LFCSP |

| ADAU1590ACPZ-RL7 | IC AMP AUDIO PWR 48LFCSP |

| ADAU1592ACPZ | IC AMP AUDIO PWR 24W 48LFCSP |

| ADAU1701JSTZ-RL | IC AUDIO PROC 2ADC/4DAC 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1446EBZ | 制造商:Analog Devices 功能描述:SIGMADSP? DIGITAL AUDIO PROCESSOR WITH FLEXIBLE AUDIO - Bulk |

| ADAU1446YSTZ-3A | 功能描述:IC SIGMADSP 175MHZ 100LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1446YSTZ-3A-RL | 功能描述:IC SIGMADSP 175MHZ 100LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1450WBCPZ | 功能描述:IC AUDIO PROCESSOR 72LFCSP 制造商:analog devices inc. 系列:SigmaDSP? 包装:托盘 零件状态:有效 类型:Sigma 接口:I2C,SPI 时钟速率:147.456MHz 非易失性存储器:- 片载 RAM:64KB 电压 - I/O:3.3V 电压 - 内核:1.20V 工作温度:-40°C ~ 105°C(TA) 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP-VQ(10x10) 标准包装:1 |

| ADAU1450WBCPZ-RL | 功能描述:IC AUDIO PROCESSOR 72LFCSP 制造商:analog devices inc. 系列:SigmaDSP? 包装:剪切带(CT) 零件状态:在售 类型:Sigma 接口:I2C,SPI 时钟速率:147.456MHz 非易失性存储器:- 片载 RAM:64KB 电压 - I/O:3.30V 电压 - 内核:1.20V 工作温度:-40°C ~ 105°C(TA) 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP-VQ(10x10) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。