- 您现在的位置:买卖IC网 > PDF目录2063 > ADAU1445YSVZ-3A-RL (Analog Devices Inc)IC SIGMADSP 175MHZ 100TQFP PDF资料下载

参数资料

| 型号: | ADAU1445YSVZ-3A-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 14/92页 |

| 文件大小: | 0K |

| 描述: | IC SIGMADSP 175MHZ 100TQFP |

| 标准包装: | 1,000 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 车载音频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-TQFP 裸露焊盘 |

| 供应商设备封装: | 100-TQFP-EP(14x14) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADAU1445/ADAU1446

Rev. A | Page 21 of 92

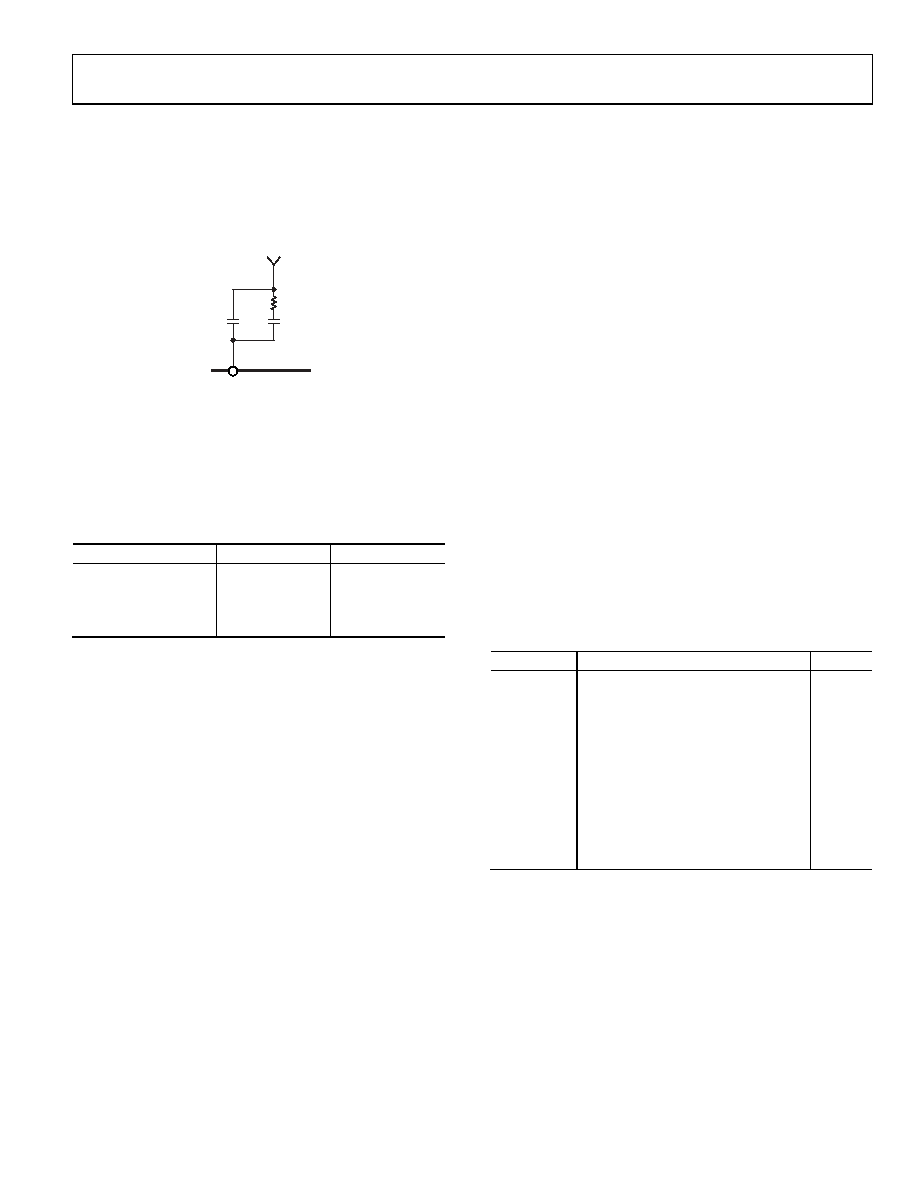

PLL Loop Filter

The PLL loop filter should be connected to the PLL_FILT pin. This

filter, shown in Figure 11, includes three passive components—

two capacitors and a resistor. The values of these components

do not need to be exact; the tolerance can be up to 10% for the

resistor and up to 20% for each capacitor. The 3.3 V signal shown

in the schematic can be connected to the PVDD supply of the chip.

ADAU1445/

ADAU1446

1.5k

PLL_FILT

33nF

1.8nF

PVDD

07

69

6-

0

11

Figure 11. PLL Loop Filter

Using the ADAU1445/ADAU1446 as Clock Masters

To output a master clock from the ADAU1445/ADAU1446 to

other chips in the system, the CLKOUT pin is used. To set the

frequency of this clock signal, the CLKMODEx pins must be set

(see Table 8).

Table 8. CLKOUT Modes

CLKOUT Signal

CLKMODE1

CLKMODE0

Disabled

0

Buffered Oscillator

0

1

256 × fS,NORMAL

1

0

512 × fS,NORMAL

1

Master Clock and PLL Modes and Settings

DSP Core Rate Select Register (Address 0xE220)

The core’s start pulse initiates the operation of the core and

determines the sample rate of signals processed inside the core.

This pulse can originate from one of three internally generated

fS signals (fS,NORMAL, fS,DUAL, or fS,QUAD), one of the 12 serial input fS

signals (an LRCLK signal associated with a serial input port),

one of the 12 serial output fS signals (an LRCLK signal associated

with a serial output port), or LRCLK recovered from the S/PDIF

receiver input.

Setting the value of the DSP core rate select register sets the speed

of the DSP core (see Table 10). By default, the signals processed

in the core are at the normal DSP core rate; therefore, the core

clock is 3584 × fS, NORMAL. For a system processing signals in the

core at the dual rate, the start pulse should be set to the internally

generated dual rate, and the core clock is 1792 × fS,DUAL. For a

system processing signals in the core at the quad rate, the start

pulse should be set to the internally generated quad rate, and

the core clock is 896 × fS,QUAD.

Master Clock Enable Switch Register (Address 0xE280)

For power-saving purposes, various parts of the chip can be

switched on and off. Setting the appropriate bit to 0 disables the

corresponding subsystem, and setting the bit to 1 enables the

subsystem. This is the first register that should be set after the

device is powered on and completes its initialization. Failure to

set this register may compromise future register writes.

Table 9. Bit Descriptions of Register 0xE280

Bit Position

Description1

Default

[15:9]

Reserved

[8]

Enable MCLK to auxiliary ADCs

0

[7]

Enable MCLK to S/PDIF transmitter

0

[6]

Enable MCLK to S/PDIF receiver

0

[5]

Enable MCLK to DSP core

0

[4]

Enable MCLK to Stereo ASRC[7:4]2

0

[3]

Enable MCLK to Stereo ASRC[3:0]2

0

[2]

Enable MCLK to serial outputs

0

[1]

Enable MCLK to serial inputs

0

[0]

Enable MCLK to flexible audio routing

matrix (FARM)

0

1 0 = disable, 1 = enable.

2 See the Flexible Audio Routing Matrix—Input Side section for more

information.

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1461WBCPZ-R7 | IC SIGMADSP 24BIT 96KHZ PLL 32 |

| ADAU1513ACPZ-RL7 | IC AMP AUDIO PWR 23W 48LFCSP |

| ADAU1590ACPZ-RL7 | IC AMP AUDIO PWR 48LFCSP |

| ADAU1592ACPZ | IC AMP AUDIO PWR 24W 48LFCSP |

| ADAU1701JSTZ-RL | IC AUDIO PROC 2ADC/4DAC 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1446EBZ | 制造商:Analog Devices 功能描述:SIGMADSP? DIGITAL AUDIO PROCESSOR WITH FLEXIBLE AUDIO - Bulk |

| ADAU1446YSTZ-3A | 功能描述:IC SIGMADSP 175MHZ 100LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1446YSTZ-3A-RL | 功能描述:IC SIGMADSP 175MHZ 100LQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1450WBCPZ | 功能描述:IC AUDIO PROCESSOR 72LFCSP 制造商:analog devices inc. 系列:SigmaDSP? 包装:托盘 零件状态:有效 类型:Sigma 接口:I2C,SPI 时钟速率:147.456MHz 非易失性存储器:- 片载 RAM:64KB 电压 - I/O:3.3V 电压 - 内核:1.20V 工作温度:-40°C ~ 105°C(TA) 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP-VQ(10x10) 标准包装:1 |

| ADAU1450WBCPZ-RL | 功能描述:IC AUDIO PROCESSOR 72LFCSP 制造商:analog devices inc. 系列:SigmaDSP? 包装:剪切带(CT) 零件状态:在售 类型:Sigma 接口:I2C,SPI 时钟速率:147.456MHz 非易失性存储器:- 片载 RAM:64KB 电压 - I/O:3.30V 电压 - 内核:1.20V 工作温度:-40°C ~ 105°C(TA) 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP-VQ(10x10) 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。