参数资料

| 型号: | ADE7116ASTZF8 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 139/152页 |

| 文件大小: | 0K |

| 描述: | IC ENERGY METER 64-LQFP |

| 产品变化通告: | Product Discontinuance 27/Oct/2011 |

| 标准包装: | 160 |

| 输入阻抗: | 770 千欧 |

| 测量误差: | 0.1% |

| 电压 - 高输入/输出: | 2V |

| 电压 - 低输入/输出: | 0.8V |

| 电流 - 电源: | 4mA |

| 电源电压: | 2.4 V ~ 3.7 V |

| 测量仪表类型: | 单相 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页当前第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页

�� ��

��

��

��ADE7116/ADE7156/ADE7166/ADE7169/ADE7566/ADE7569�

�I� 2� C-COMPATIBLE� INTERFACE�

�The� ADE7116/ADE7156/ADE7166/ADE7169/ADE7566/�

�The� bit� rate� is� defined� in� the� I2CMOD� SFR� as� follows:�

�ADE7569� support� a� fully� licensed� I� 2� C� interface.� The� I� 2� C�

�interface� is� implemented� as� a� full� hardware� master.�

�f� SCLK� =�

�f� CORE�

�16� � 2� I� 2� CR� [� 1� :� 0� ]�

�SDATA� (P0.4/MOSI/SDATA)� is� the� data� I/O� pin,� and� SCLK�

�(P0.6/SCLK/T0)� is� the� serial� clock.� These� two� pins� are� shared�

�with� the� MOSI� and� SCLK� pins� of� the� on-chip� SPI� interface.�

�Therefore,� the� user� can� enable� only� one� interface� or� the� other�

�on� these� pins� at� any� given� time.� The� SCPS� bit� (Bit� 5)� in� the�

�configuration� SFR� (CFG,� Address� 0xAF)� selects� which�

�peripheral� is� active.�

�The� two� pins� used� for� data� transfer,� SDATA� and� SCLK,� are�

�SLAVE� ADDRESSES�

�The� I� 2� C� slave� address� SFR� (I2CADR,� Address� 0xE9)� contains�

�the� slave� device� ID.� The� LSB� of� this� register� contains� a�

�read/write� request.� A� write� to� this� SFR� starts� the� I� 2� C�

�communication.�

�I� 2� C� REGISTERS�

�The� I� 2� C� peripheral� interface� consists� of� five� SFRs:�

�configured� in� a� wire-AND� format� that� allows� arbitration� in�

�a� multimaster� system.�

�The� transfer� sequence� of� an� I� 2� C� system� consists� of� a� master� device�

�initiating� a� transfer� by� generating� a� start� condition� while� the� bus�

�is� idle.� The� master� transmits� the� address� of� the� slave� device� and�

�the� direction� of� the� data� transfer� in� the� initial� address� transfer.� If�

�?�

�?�

�?�

�?�

�?�

�I2CMOD�

�SPI2CSTAT�

�I2CADR�

�SPI2CTx�

�SPI2CRx�

�the� slave� acknowledges,� the� data� transfer� is� initiated.� This� continues�

�until� the� master� issues� a� stop� condition� and� the� bus� becomes� idle.�

�SERIAL� CLOCK� GENERATION�

�The� I� 2� C� master� in� the� system� generates� the� serial� clock� for� a�

�transfer.� The� master� channel� can� be� configured� to� operate� in�

�fast� mode� (256� kHz)� or� standard� mode� (32� kHz).�

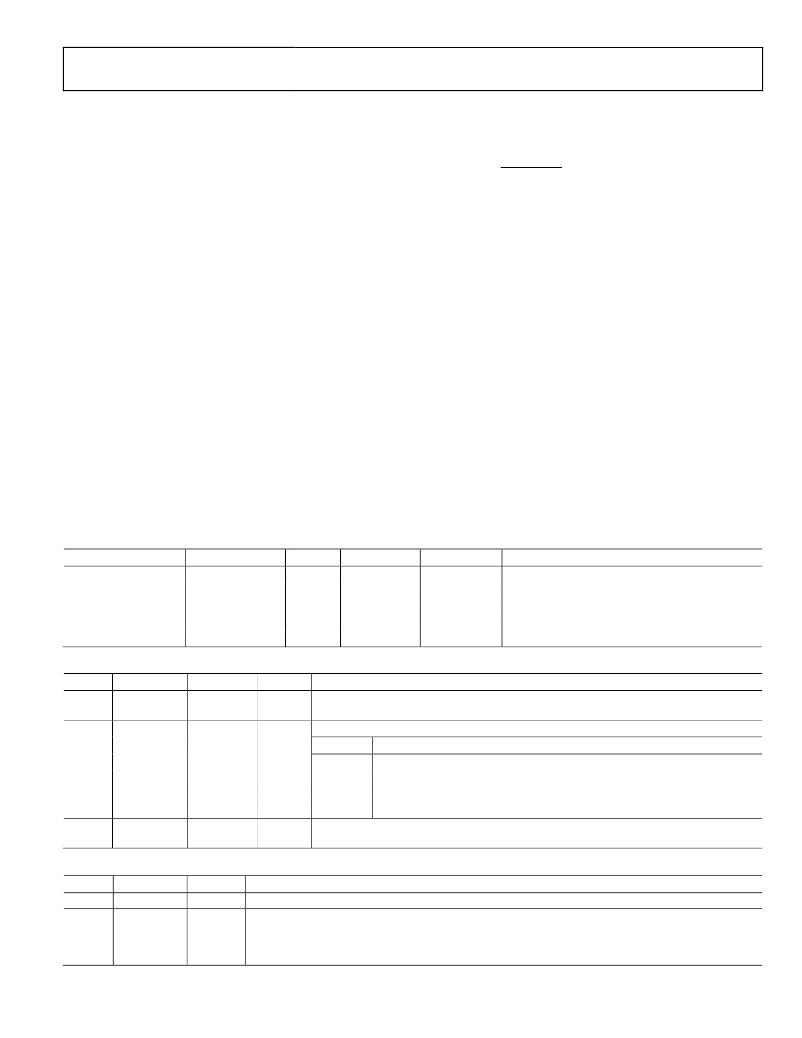

�Table� 151.� I� 2� C� SFR� List�

�Because� the� SPI� and� I� 2� C� serial� interfaces� share� the� same� pins,�

�they� also� share� the� same� SFRs,� such� as� the� SPI2CTx� and� SPI2CRx�

�SFRs.� In� addition,� the� I2CMOD,� I2CADR,� and� SPI2CSTAT,� and�

�SPI2CTx� SFRs� are� shared� with� the� SPIMOD1,� SPIMOD2,� and�

�SPISTAT� SFRs,� respectively.�

�SFR� Address�

�0x9A�

�0x9B�

�0xE8�

�0xE9�

�0xEA�

�Mnemonic�

�SPI2CTx�

�SPI2CRx�

�I2CMOD�

�I2CADR�

�SPI2CSTAT�

�R/W�

�W�

�R�

�R/W�

�R/W�

�R/W�

�Length�

�8�

�8�

�8�

�8�

�8�

�Default�

�0�

�0�

�0�

�0�

�Description�

�SPI/I� 2� C� transmit� buffer� (see� Table� 146).�

�SPI/I� 2� C� receive� buffer� (see� Table� 147).�

�I� 2� C� mode� (see� Table� 152).�

�I� 2� C� slave� address� (see� Table� 153).�

�I� 2� C� interrupt� status� register� (see� Table� 154).�

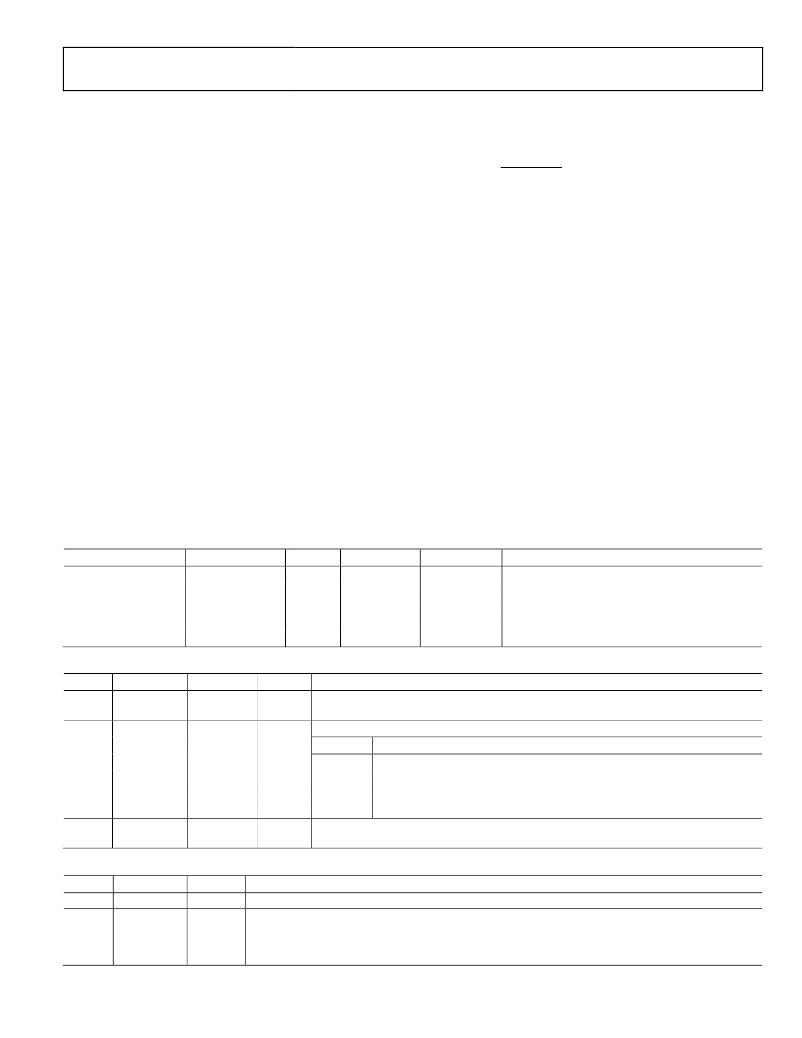

�Table� 152.� I� 2� C� Mode� SFR� (I2CMOD,� Address� 0xE8)�

�Bit�

�7�

�Bit� Address�

�0xEF�

�Mnemonic�

�I2CEN�

�Default�

�0�

�Description�

�I� 2� C� enable� bit.� When� this� bit� is� set� to� Logic� 1,� the� I� 2� C� interface� is� enabled.� A� write� to� the�

�I2CADR� SFR� starts� a� communication.�

�[6:5]�

�0xEE� to� 0xED�

�I2CR�

�0�

�I� 2� C� SCLK� frequency.�

�I2CR�

�00�

�01�

�10�

�11�

�Result�

�f� CORE� /16� =� 256� kHz� if� f� CORE� =� 4.096� MHz.�

�f� CORE� /32� =� 128� kHz� if� f� CORE� =� 4.096� MHz.�

�f� CORE� /64� =� 64� kHz� if� f� CORE� =� 4.096� MHz.�

�f� CORE� /128� =� 32� kHz� if� f� CORE� =� 4.096� MHz.�

�[4:0]�

�0xEC� to� 0xE8�

�I2CRCT�

�0�

�Configures� the� length� of� the� I� 2� C� received� FIFO� buffer.� The� I� 2� C� peripheral� stops� when� the�

�I2CRCT� bits� +� 1� byte� have� been� read,� or� if� an� error� occurs.�

�Table� 153.� I� 2� C� Slave� Address� SFR� (I2CADR,� Address� 0xE9)�

�Bit�

�[7:1]�

�0�

�Mnemonic�

�I2CSLVADR�

�I2CR_W�

�Default�

�0�

�0�

�Description�

�Address of the I� 2� C slave being addressed. Writing to this register starts the I� 2� C transmission (read or write).�

�Command� bit� for� read� or� write.� When� this� bit� is� set� to� Logic� 1,� a� read� command� is� transmitted� on� the�

�I� 2� C� bus.� Data� from� the� slave� in� the� SPI2CRx� SFR� (Address� 0x9B)� is� expected� after� a� command� byte.�

�When� this� bit� is� set� to� Logic� 0,� a� write� command� is� transmitted� on� the� I� 2� C� bus.� Data� to� slave� is� expected�

�in� the� SPI2CTx� SFR.�

�Rev.� B� |� Page� 139� of� 1� 52�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADE5166ASTZF62-RL | IC METER/8052/RTC/LCD DRV 64LQFP |

| ADE5166ASTZF62 | IC METER/8052/RTC/LCD DRV 64LQFP |

| NCP699SN28T1G | IC REG LDO 2.8V 240MA 5TSOP |

| RSC50DRYN-S13 | CONN EDGECARD 100POS .100 EXTEND |

| LFEC3E-4QN208I | IC FPGA 3.1KLUTS 208PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADE7116ASTZF8-RL | 功能描述:IC ENERGY METER 64-LQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

| ADE7156ASTZF16 | 功能描述:IC ENERGY METER 64-LQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

| ADE7156ASTZF16-RL | 功能描述:IC ENERGY METER 64-LQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

| ADE7156ASTZF8 | 功能描述:IC ENERGY METER 64-LQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

| ADE7156ASTZF8-RL | 功能描述:IC ENERGY METER 64-LQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:* |

发布紧急采购,3分钟左右您将得到回复。