- 您现在的位置:买卖IC网 > Datasheet目录309 > ADZS-BF561-EZLITE (Analog Devices Inc)BOARD EVAL ADSP-BF561 Datasheet资料下载

参数资料

| 型号: | ADZS-BF561-EZLITE |

| 厂商: | Analog Devices Inc |

| 文件页数: | 12/64页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL ADSP-BF561 |

| 产品培训模块: | Interfacing AV Converters to Blackfin Processors Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services |

| 特色产品: | Blackfin? BF50x Series Processors |

| 标准包装: | 1 |

| 系列: | Blackfin® |

| 类型: | DSP |

| 适用于相关产品: | ADSP-BF561 |

| 所含物品: | 评估板、软件和说明文档 |

| 配用: | ADZS-USBLAN-EZEXT-ND - BOARD DAUGHTER EXTENDED USB-LAN ADZS-BFFPGA-EZEXT-ND - BOARD EVAL FPGA BLACKFIN EXTENDR ADZS-BF-EZEXT-1-ND - BOARD DAUGHTER ADSP-BF533/561KIT |

| 相关产品: | ADSP-BF561SKBCZ-6V-ND - IC DSP 32BIT 600MHZ 256CSPBGA ADSP-BF561SKBCZ-5V-ND - IC DSP 32BIT 500MHZ 256CSPBGA ADSP-BF561SKBCZ-5A-ND - IC DSP CTLR 32BIT BKFN 256CSPBGA ADSP-BF561SKBCZ-6A-ND - IC DSP CTRLR 32B 600MHZ 256CPBGA ADSP-BF561SBBCZ-5A-ND - IC DSP CTRLR 32B 500MHZ 256CPBGA ADSP-BF561SBBZ500-ND - IC PROCESSOR 500MHZ 297-PBGA ADSP-BF561SBBZ600-ND - IC DSP 32BIT 600MHZ 297-BGA ADSP-BF561SKBZ600-ND - IC DSP 32BIT 600MHZ 297PBGA ADSP-BF561SKBZ500-ND - IC DSP 32BIT 500MHZ 297PBGA ADSP-BF561SKB600-ND - IC DSP CTRLR 32BIT 600MHZ 297BGA 更多... |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

�� �

�

�

�ADSP-BF561 �

�regulator� for� the� processor� can� be� shut� off� by� writing� b#00� to� the�

�FREQ� bits� of� the� VR_CTL� register.� This� disables� both� CCLK�

�and� SCLK.� Furthermore,� it� sets� the� internal� power� supply� volt-�

�age� (V� DDINT� )� to� 0� V� to� provide� the� lowest� static� power� dissipation.�

�Any� critical� information� stored� internally� (memory� contents,�

�register� contents,� etc.)� must� be� written� to� a� nonvolatile� storage�

�device� prior� to� removing� power� if� the� processor� state� is� to� be�

�preserved.� Since� V� DDEXT� is� still� supplied� in� this� mode,� all� of� the�

�external� pins� three-state,� unless� otherwise� specified.� This� allows�

�other� devices� that� may� be� connected� to� the� processor� to� have�

�power� still� applied� without� drawing� unwanted� current.� The�

�interna� l� supply� regulator� can� be� woken� up� by� asserting� the�

�RESET� pin.�

�Power� Savings�

�As� shown� in� Table� 4� ,� the� ADSP-BF561� supports� two� different�

�power� domains.� The� use� of� multiple� power� domains� maximizes�

�flexibility,� while� maintaining� compliance� with� industry� stan-�

�dards� and� conventions.� By� isolating� the� internal� logic� of� the�

�ADSP-BF561� into� its� own� power� domain,� separate� from� the� I/O,�

�the� processor� can� take� advantage� of� Dynamic� Power� Manage-�

�ment,� without� affecting� the� I/O� devices.� There� are� no�

�sequencing� requirements� for� the� various� power� domains.�

�Table� 4.� ADSP-BF561� Power� Domains�

�t� NOM� is� the� duration� running� at� f� CCLKNOM�

�t� RED� is� the� duration� running� at� f� CCLKRED�

�The� percent� power� savings� is� calculated� as:�

�%� power� savings� =� (� 1� –� power� savings� factor� )� ×� 100%�

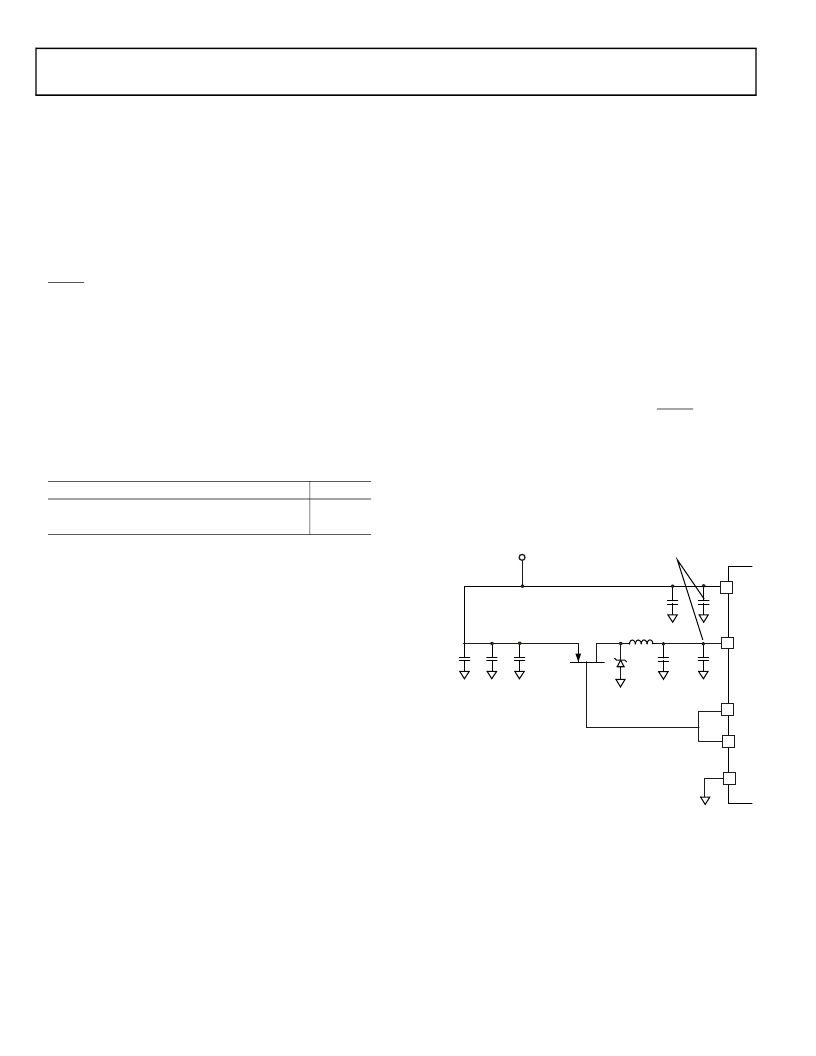

�VOLTAGE� REGULATION�

�The� ADSP-BF561� processor� provides� an� on-chip� voltage� regula-�

�tor� that� can� generate� appropriate� V� DDINT� voltage� levels� from� the�

�V� DDEXT� supply.� See� Operating� Conditions� on� Page� 20� for� regula-�

�tor� tolerances� and� acceptable� V� DDEXT� ranges� for� specific� models.�

��complete� the� power� management� system.� The� regulator� con-�

�trols� the� internal� logic� voltage� levels� and� is� programmable� with�

�the� voltage� regulator� control� register� (VR_CTL)� in� increments�

�of� 50� mV.� To� reduce� standby� power� consumption,� the� internal�

�voltage� regulator� can� be� programmed� to� remove� power� to� the�

�processor� core� while� keeping� I/O� power� (V� DDEXT� )� supplied.� While�

�in� the� hibernate� state,� V� DDEXT� can� still� be� applied,� thus� eliminating�

�the� need� for� external� buffers.� The� voltage� regulator� can� be� acti-�

�vated� from� this� power-down� state� by� asserting� RESET,� which�

�will� then� initiate� a� boot� sequence.� The� regulator� can� also� be� dis-�

�abled� and� bypassed� at� the� user’s� discretion.�

�The� internal� voltage� regulation� feature� is� not� available� on� any� of�

�Power� Domain�

�All� internal� logic�

�I/O�

�V� DD� Range�

�V� DDINT�

�V� DDEXT�

�the� 600� MHz� speed� grade� models� or� automotive� grade� models.�

�External� voltage� regulation� is� required� to� ensure� correct� opera-�

�tion� of� these� parts� at� 600� MHz.�

�The� power� dissipated� by� a� processor� is� largely� a� function� of� the�

�clock� frequency� of� the� processor� and� the� square� of� the� operating�

�V� DDEXT�

�(LOW-INDUCTANCE) �

�SET� OF� DECOUPLING �

�CAPACITORS�

�voltage.� For� example,� reducing� the� clock� frequency� by� 25%�

�results� in� a� 25%� reduction� in� dynamic� power� dissipation,� while�

�reducing� the� voltage� by� 25%� reduces� dynamic� power� dissipation�

�100μF�

�+�

�V� DDEXT�

�by� more� than� 40%.� Further,� these� power� savings� are� additive,� in�

�100nF�

�10μH�

�that� if� the� clock� frequency� and� supply� voltage� are� both� reduced,�

�the� power� savings� can� be� dramatic.�

�100μF�

�+�

�+�

�V� DDINT�

�The� dynamic� power� management� feature� of� the� ADSP-BF561�

�allows� both� the� processor’s� input� voltage� (V� DDINT� )� and� clock� fre-�

�quency� (f� CCLK� )� to� be� dynamically� controlled.�

�10μF�

�LOW� ESR�

�FDS9431A�

�ZHCS1000�

�100μF�

�VR� OUT�

�The� savings� in� power� dissipation� can� be� modeled� using� the�

�=� ---------------------� � ?� ?� --------------------------� ?� ?� � ??� -----------� ??�

�power� savings� factor� and� %� power� savings� calculations.�

�The� power� savings� factor� is� calculated� as:�

�power� savings� factor�

�f� CCLKRED� V� DDINTRED� 2� t� RED�

�f� CCLKNOM� V� DDINTNOM� t� NOM�

�where� the� variables� in� the� equations� are:�

�f� CCLKNOM� is� the� nominal� core� clock� frequency�

�f� CCLKRED� is� the� reduced� core� clock� frequency�

�V� DDINTNOM� is� the� nominal� internal� supply� voltage�

�V� DDINTRED� is� the� reduced� internal� supply� voltage�

�SHORT� AND� LOW-�

�INDUCTANCE� WIRE�

�NOTE:� DESIGNER� SHOULD� MINIMIZE�

�TRACE� LENGTH� TO� FDS9431A.�

�Figure� 4.� Voltage� Regulator� Circuit�

�Voltage� Regulator� Layout� Guidelines�

�Regulator� external� component� placement,� board� routing,� and�

�bypass� capacitors� all� have� a� significant� effect� on� noise� injected�

�into� the� other� analog� circuits� on-chip.� The� VROUT1–0� traces�

�and� voltage� regulator� external� components� should� be� consid-�

�ered� as� noise� sources� when� doing� board� layout� and� should� not�

�VR� OUT�

�GND�

�be� routed� or� placed� near� sensitive� circuits� or� components� on� the�

�Rev.� E� |�

�Page� 12� of� 64� |�

�September� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADZS-BF592-EZLITE | KIT EVAL EZ LITE ADZS-BF592 |

| ADZS-BF609-EZBRD | KIT EVAL EZ-BOARD ADSP-BF60X |

| ADZS-HPUSB-ICE | TOOL EMULATOR USB HP CROSSCORE |

| ADZS-ICE-100B | EMULATOR BLACKFIN |

| AK-Y1301 | CABLE SCSI-3 EXTENSION 68CONDUCT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADZS-BF561-MMSKIT | 功能描述:KIT STARTER MULTIMEDIA BF561 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF) |

| ADZS-BF561-MMSKIT | 制造商:Analog Devices 功能描述:MEDIA KIT ((NW)) |

| ADZS-BF592-EZLITE | 功能描述:KIT EVAL EZ LITE ADZS-BF592 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| ADZS-BF592-EZLITE | 制造商:Analog Devices 功能描述:ADZS-BF592-EZLITE |

| ADZS-BF608-EZLITE | 制造商:Analog Devices 功能描述:DIGITAL SIGNAL PROCESSOR - DEVELOPMENT TOOL |

发布紧急采购,3分钟左右您将得到回复。