参数资料

| 型号: | ATMEGA103-6AI |

| 厂商: | Atmel |

| 文件页数: | 58/141页 |

| 文件大小: | 0K |

| 描述: | IC MCU 128K 6MHZ A/D IT 64TQFP |

| 产品培训模块: | megaAVR Introduction |

| 标准包装: | 90 |

| 系列: | AVR® ATmega |

| 核心处理器: | AVR |

| 芯体尺寸: | 8-位 |

| 速度: | 6MHz |

| 连通性: | SPI,UART/USART |

| 外围设备: | POR,PWM,WDT |

| 输入/输出数: | 32 |

| 程序存储器容量: | 128KB(64K x 16) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 4K x 8 |

| RAM 容量: | 4K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 4 V ~ 5.5 V |

| 数据转换器: | A/D 8x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 64-TQFP |

| 包装: | 托盘 |

| 配用: | ATSTK501-ND - ADAPTER KIT FOR 64PIN AVR MCU |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页

23

ATmega103(L)

0945I–AVR–02/07

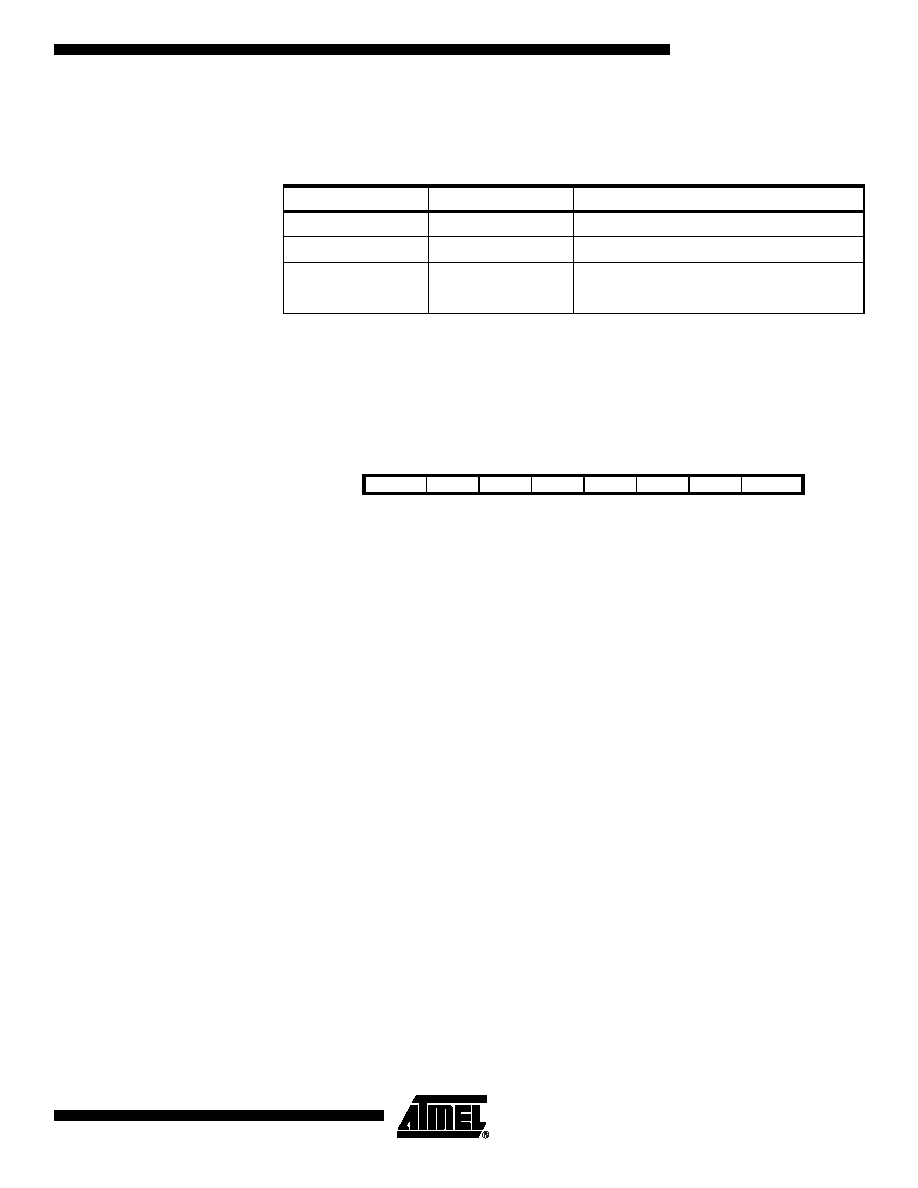

Bits 4, 3 – SM1/SM0: Sleep Mode Select Bits 1 and 0

This bit selects between the three available sleep modes as shown in Table 3.

Bits 2..0 – Res: Reserved Bits

These bits are reserved bits in the ATmega103(L) and always read as zero.

XTAL Divide Control Register

– XDIV

The XTAL Divide Control Register is used to divide the XTAL clock frequency by a num-

ber in the range 1 - 129. This feature can be used to decrease power consumption when

the requirement for processing power is low.

Bit 7 – XDIVEN: XTAL Divide Enable

When the XDIVEN bit is set (one), the clock frequency of the CPU and all peripherals is

divided by the factor defined by the setting of XDIV6 - XDIV0. This bit can be set and

cleared run-time to vary the clock frequency as suitable to the application.

Bits 6..0 – XDIV6..XDIV0: XTAL Divide Select Bits 6 - 0

These bits define the division factor that applies when the XDIVEN bit is set (one). If the

value of these bits is denoted d, the following formula defines the resulting CPU clock

frequency f

clk:

The value of these bits can only be changed when XDIVEN is zero. When XDIVEN is

set to one, the value written simultaneously into XDIV6..XDIV0 is taken as the division

factor. When XDIVEN is cleared to zero, the value written simultaneously into

XDIV6..XDIV0 is rejected. As the divider divides the Master Clock Input to the MCU, the

speed of all peripherals is reduced when a division factor is used.

Reset and Interrupt

Handling

The ATmega103(L) provides 23 different interrupt sources. These interrupts and the

separate Reset Vector each have a separate Program Vector in the Program memory

space. All interrupts are assigned individual enable bits that must be set (one) together

with the I-bit in the Status Register in order to enable the interrupt.

The lowest addresses in the Program memory space are automatically defined as the

Reset and Interrupt Vectors. The complete list of vectors is shown in Table 4. The list

also determines the priority levels of the different interrupts. The lower the address, the

Table 3. Sleep Mode Select

SM1

SM0

Sleep Mode

0

Idle mode

01

Reserved

10

Power-down

11

Power-save

Bit

7

65

43

21

0

$3C ($5C)

XDIVEN

XDIV6

XDIV5

XDIV4

XDIV3

XDIV2

XDIV1

XDIV0

XDIV

Read/Write

R/W

Initial Value

0

f

CLK

XTAL

129

d

–

-------------------

=

相关PDF资料 |

PDF描述 |

|---|---|

| ATMEGA128A-AUR | MCU AVR 128K FLASH 16MHZ 64TQFP |

| ATMEGA128L-8MJ | IC MCU AVR 128K 8MHZ LV 64-QFN |

| ATMEGA16-16MUR | MCU AVR 16KB FLASH 16MHZ 44QFN |

| ATMEGA164PA-AN | IC MCU AVR 16K FLASH 44TQFP |

| ATMEGA164PA-CUR | MCU AVR 16KB FLASH 20MHZ 49VFBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ATMEGA103L | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 128K Bytes In-System Programmable Flash |

| ATMEGA103L-4AC | 功能描述:8位微控制器 -MCU TQFP-64 128K FLASH 3 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ATMEGA103L-4AI | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-Bit Microcontroller with 64K/128K Bytes In-System Programmable Flash |

| ATMEGA128 | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 128K Bytes In-System Programmable Flash |

| ATMEGA128(L) | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ATmega128(L) Preliminary Summary [Updated 9/03. 23 Pages] |

发布紧急采购,3分钟左右您将得到回复。