参数资料

| 型号: | DS3106LN+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 41/92页 |

| 文件大小: | 0K |

| 描述: | IC TIMING LINE CARD 64-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 160 |

| 类型: | 定时卡 IC,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum,电信 |

| 输入: | CMOS,TTL |

| 输出: | CMOS,LVDS,LVPECL,TTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 312.5MHz |

| 电源电压: | 1.62 V ~ 1.98 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-LQFP |

| 供应商设备封装: | 64-LQFP(10x10) |

| 包装: | 托盘 |

| 产品目录页面: | 1429 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

DS3106

46

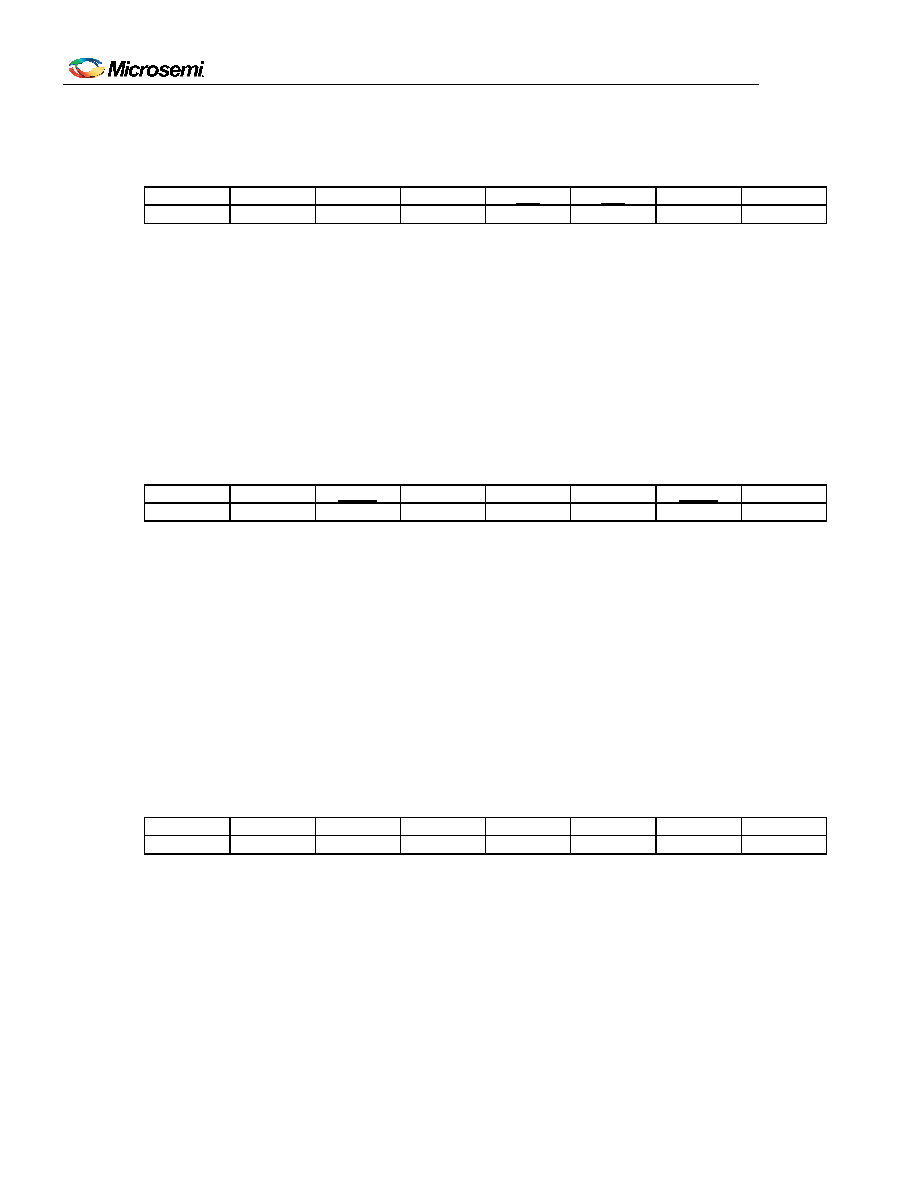

Register Name:

VALSR1

Register Description:

Input Clock Valid Status Register 1

Register Address:

0Eh

Bit #

7

6

5

4

3

2

1

0

Name

—

IC4

IC3

—

Default

0

Bits 3 and 2: Input Clock Valid Status (IC[3:2]). Each of these real-time status bits is set to 1 when the

corresponding input clock is valid. An input is valid if it has no active alarms (ACT = 0 in the ISR2 register). See

0 = Invalid

1 = Valid

Register Name:

ISR2

Register Description:

Input Status Register 2

Register Address:

11h

Bit #

7

6

5

4

3

2

1

0

Name

—

ACT4

—

ACT3

—

Default

0

1

0

1

0

Bit 5: Activity Alarm for Input Clock 4 (ACT4). This real-time status bit is set to 1 when the leaky bucket

accumulator for IC4 reaches the alarm threshold specified in the LBxU register (where x in LBxU is specified in the

BUCKET field of ICR4). An activity alarm clears the IC4 status bit in the VALSR1 register, invalidating the IC4

clock. See Section 7.5.2.

Bit 1: Activity Alarm for Input Clock 3 (ACT3). This bit has the same behavior as the ACT4 bit but for the IC3

input clock.

Register Name:

MSR4

Register Description:

Master Status Register 4

Register Address:

17h

Bit #

7

6

5

4

3

2

1

0

Name

—

HORDY

MRAA

—

Default

0

Bit 6: Holdover Frequency Ready (HORDY). This latched status bit is set to 1 when the T0 DPLL has a holdover

value that has been averaged over the one-second holdover averaging period. HORDY is cleared when written

with a 1. When HORDY is set it can cause an interrupt request on the INTREQ pin if the HORDY interrupt enable

Bit 5: Multiregister Access Aborted (MRAA). This latched status bit is set to 1 when a multibyte access (read or

write) is interrupted by another access to the device. MRAA is cleared when written with a 1. MRAA cannot cause

an interrupt to occur. See Section 8.3.

相关PDF资料 |

PDF描述 |

|---|---|

| DS3231MZ+ | IC RTC I2C 8SOIC |

| DS3231SN#T&R | IC RTC W/TCXO 16-SOIC |

| DS3232MZ+ | IC RTC W/SRAM I2C 8SOIC |

| DS3232SN#T&R | IC RTC W/TCXO 20-SOIC |

| DS3234S# | IC RTC W/TCXO 20-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3106LN+ | 功能描述:计时器和支持产品 Line Card Timing IC RoHS:否 制造商:Micrel 类型:Standard 封装 / 箱体:SOT-23 内部定时器数量:1 电源电压-最大:18 V 电源电压-最小:2.7 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装:Reel |

| DS3107FP000 | 制造商:Thomas & Betts 功能描述:30A,CON,2P3W,MG,107,125V |

| DS3107FRAB0 | 制造商:Thomas & Betts 功能描述:30A,REC,2P3W,MG,107,AB0,125,SC |

| DS3107MP000 | 制造商:Thomas & Betts 功能描述:30A,PLG,2P3W,MG,107,125V |

| DS3107MP00K | 制造商:Thomas & Betts 功能描述:30A,PLG,2P3W,MG,107,125V,CC |

发布紧急采购,3分钟左右您将得到回复。