- 您现在的位置:买卖IC网 > PDF目录11560 > DS3148N (Maxim Integrated Products)IC 8CH DS3/3 FRAMER 349-BGA PDF资料下载

参数资料

| 型号: | DS3148N |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 11/89页 |

| 文件大小: | 0K |

| 描述: | IC 8CH DS3/3 FRAMER 349-BGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 控制器类型: | DS3/E3 调帧器 |

| 接口: | LIU |

| 电源电压: | 3.135 V ~ 3.465 V |

| 电流 - 电源: | 640mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 349-BGA 裸露焊盘 |

| 供应商设备封装: | 349-HCBGA(27x27) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

DS3146/DS3146/DS31412 6-/8-/12-Channel DS3/E3 Framers

19 of 89

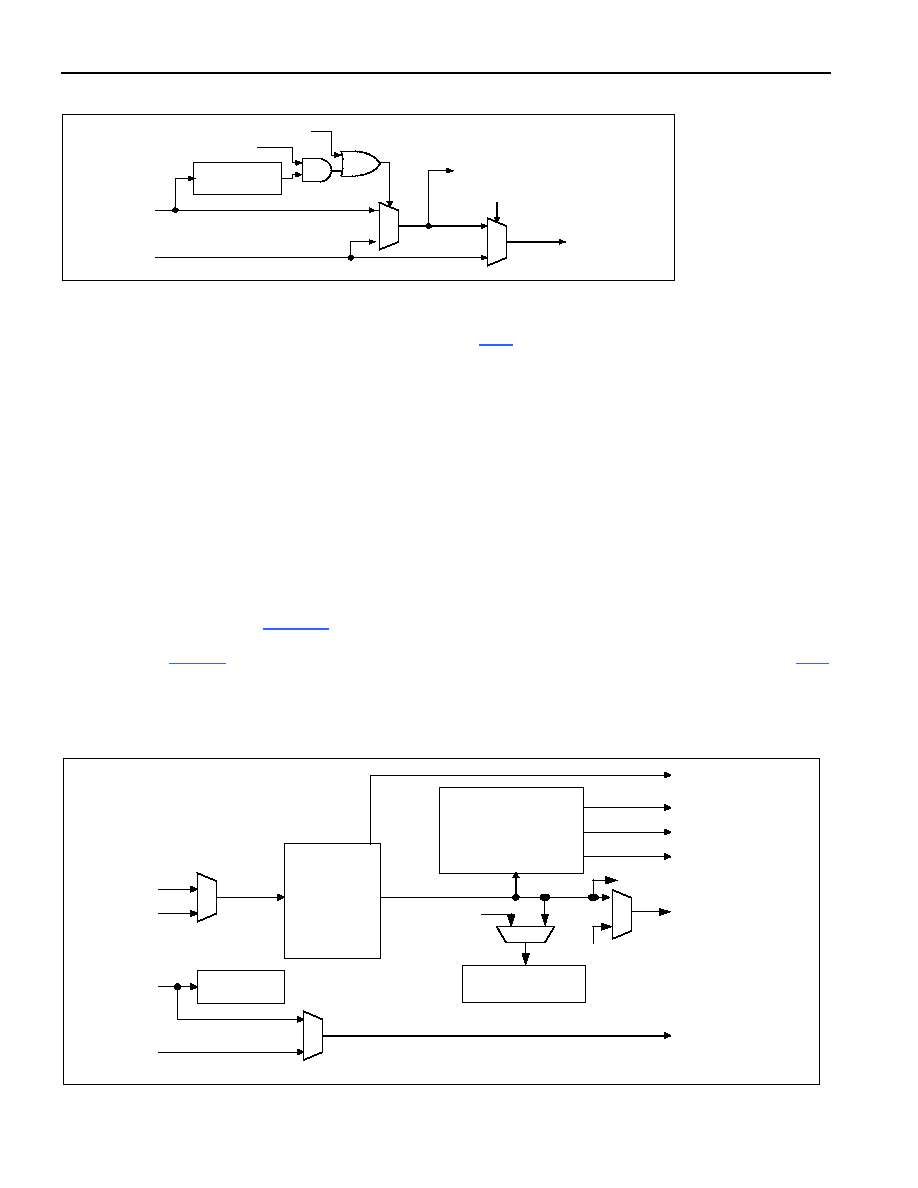

Figure 7-2. Transmit Clock Block Diagram

7.2.2 Loss-of-Clock Detection

The LOTC and LORC (loss-of-receive clock) status bits in the MSR register are set when the transmit (TICLK) and

receive (RCLK) clocks are stopped, respectively. The clocks are monitored with the system clock (SCLK), which

must be running for the loss-of-clock circuits to function properly. The LOTC and LORC status bits are set when

TICLK or RCLK have been stopped high or low for between 9 and 21 clock periods (depending on SCLK

frequency). The LOTC and LORC status bits are cleared after the device detects a few edges of the monitored

clock.

7.3 Receiver Logic

In the normal operating mode, the signals on RPOS and RNEG are decoded as an HDB3 signal in E3 mode or as

a B3ZS signal in DS3 mode and output on the RDAT pin. The input signal is monitored for loss-of-signal, bipolar

violations, excessive zeros, AIS, unframed all ones and, after decoding, is sent to the BERT and synchronizer.

When the synchronizer finds the framing pattern in the overhead bits, it clears the out-of-frame indication (ROOF)

and aligns the start-of-frame (RSOF) and data-enable (RDEN) signals to the signal on RDAT. If the framing pattern

is lost, then ROOF is set and the framing pattern is searched for again. While the framing pattern is being searched

for, the RSOF and RDEN signals maintain the alignment with the last known position of the framing pattern. If a

framing pattern is found in a new position, the RSOF and RDEN signals align with the new pattern position and the

COFAL status bit is set in the T3E3SRL register. After reset, the RSOF and RDEN signals are generated, but have

no relationship with any framing pattern until one is found. The signal on the ROOF pin can be monitored using the

OOF bit in the T3E3SR register. When the diagnostic loopback mode is enabled using the DLB bit in the MC2

register, RCLK, RPOS, and RNEG are replaced with TICLK, TPOS, and TNEG. This allows the framer and

synchronizer logic to be checked in order to isolate a problem in the system. The BERT can monitor either the

payload or the entire signal for expected test patterns.

Figure 7-3. Receiver Block Diagram

LOTC

RCLK

TCLK

TICLK

INTERNAL TCLK

LOTCMC

LLB

PLB

0

1

LORC

Rx BERT

DS3

E3 G.751

SYNCHRONIZER

HDB

B3ZS

AMI

DECODER

RPOS

RNEG

TICLK

RCLK

ROCLK

FROM Tx DLB

DLB

RDAT

RLOS

ROOF

RSOF

RDEN

FROM Tx BERT

TDAT

TO PLB MUX

相关PDF资料 |

PDF描述 |

|---|---|

| VI-24K-IX-S | CONVERTER MOD DC/DC 40V 75W |

| PIC16C54C-20E/SO | IC MCU OTP 512X12 18SOIC |

| PIC16C54C-04E/SS | IC MCU OTP 512X12 20SSOP |

| PIC12C509T-04/SM | IC MCU OTP 1KX12 8-SOIJ |

| PIC12C508T-04I/SM | IC MCU OTP 512X12 8-SOIJ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS315 | 制造商:Hubbell Wiring Device-Kellems 功能描述:SWITCH, DECO SER, 3W, 15A 120/277V, BR |

| DS3150 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V, DS3/E3/STS-1 Line Interface Unit |

| DS3150DK | 功能描述:网络开发工具 DS3150 Dev Kit RoHS:否 制造商:Rabbit Semiconductor 产品:Development Kits 类型:Ethernet to Wi-Fi Bridges 工具用于评估:RCM6600W 数据速率:20 Mbps, 40 Mbps 接口类型:802.11 b/g, Ethernet 工作电源电压:3.3 V |

| DS3150G | 功能描述:IC LIU T3/E3/STS-1 49-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

| DS3150GN | 功能描述:IC LIU T3/E3/STS-1 IND 49-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。