- 您现在的位置:买卖IC网 > PDF目录11560 > DS3148N (Maxim Integrated Products)IC 8CH DS3/3 FRAMER 349-BGA PDF资料下载

参数资料

| 型号: | DS3148N |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 9/89页 |

| 文件大小: | 0K |

| 描述: | IC 8CH DS3/3 FRAMER 349-BGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 控制器类型: | DS3/E3 调帧器 |

| 接口: | LIU |

| 电源电压: | 3.135 V ~ 3.465 V |

| 电流 - 电源: | 640mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 349-BGA 裸露焊盘 |

| 供应商设备封装: | 349-HCBGA(27x27) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

DS3146/DS3146/DS31412 6-/8-/12-Channel DS3/E3 Framers

17 of 89

6.1 Status Register Description

There are two types of bits used to build the status and information registers. The real-time status register bit

indicates the state of the corresponding signal at the time it was read. The latched status register bit is set when

the corresponding signal changes state (low-to-high, high-to-low, or both, depending on the bit). The latched status

bit is cleared when written with logic 1 and is not set again until the corresponding signal changes state again.

The following is example host-processor pseudocode that checks to see if the BERT SYNC status has changed:

If ((BSRL and 01h) neq 0) then

// SYNCL bit is set

BSRL = 01h

// Clear SYNCL bit only

If ((BSR and 01h) neq 0) then

// BERT has changed to in sync

–––––

Else

// BERT has changed to out of sync

–––––

There are four suffixes used for status and information register names: SR for real-time status registers, SRL for

latched status registers, SRIE for interrupt-enable registers, and IR for information registers. Latched status bits

have the suffix “L” and interrupt-enable bits have the suffix “IE.” The bits in the SR, SRL, and SRIE registers are

arranged such that related real-time status, latched status, and interrupt-enable bits are located in the same bit

position in neighboring registers. For example, Table 6-B shows that the real-time status bit SYNC, the latched

status bit SYNCL, and the interrupt-enable bit SYNCIE are all located in bit 0 of their respective registers (BSR,

BSRL, and BSRIE).

When set, most latched status register bits can cause an interrupt on the

INT pin if the corresponding interrupt-

enable register bit is also set. Most latched status register bits have an associated real-time status register bit.

Information registers can contain a mix of real-time and latched status bits, none of which can cause an interrupt.

Table 6-B. Status Register Set Example

REGISTER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

N/A

RA1

RA0

N/A

BBCO

BECO

SYNC

N/A

RA1L

RA0L

BEDL

BBCOL

BECOL

SYNCL

N/A

BEDIE

BBCOIE

BECOIE

SYNCIE

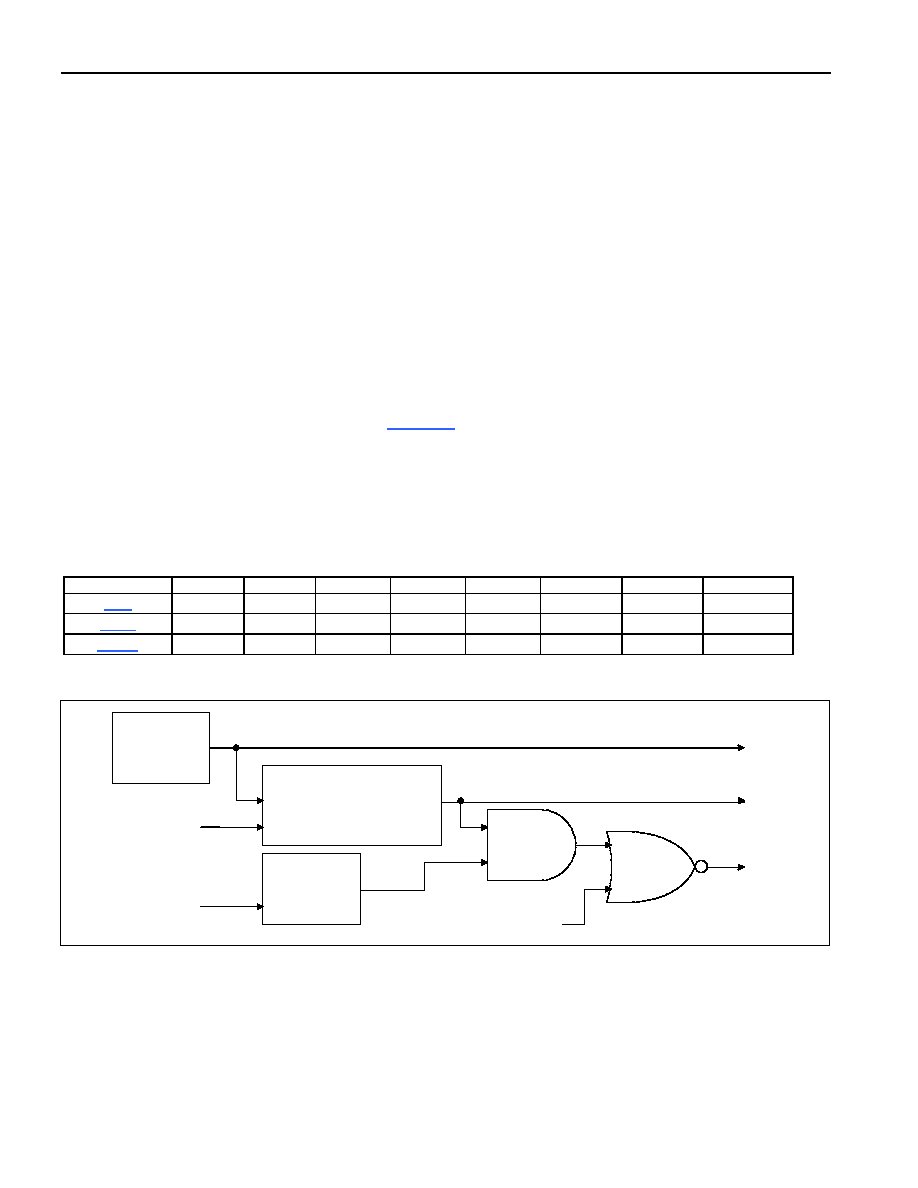

Figure 6-1. Status Register Interrupt Flow

WR

EVENT

LATCHED STATUS REGISTER

SET ON EVENT DETECT

CLEAR ON WRITE LOGIC 1

INT ENABLE

REGISTER

SR

SRL

INT

OTHER INT

SOURCE

REAL-TIME STATUS

LATCHED STATUS

相关PDF资料 |

PDF描述 |

|---|---|

| VI-24K-IX-S | CONVERTER MOD DC/DC 40V 75W |

| PIC16C54C-20E/SO | IC MCU OTP 512X12 18SOIC |

| PIC16C54C-04E/SS | IC MCU OTP 512X12 20SSOP |

| PIC12C509T-04/SM | IC MCU OTP 1KX12 8-SOIJ |

| PIC12C508T-04I/SM | IC MCU OTP 512X12 8-SOIJ |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS315 | 制造商:Hubbell Wiring Device-Kellems 功能描述:SWITCH, DECO SER, 3W, 15A 120/277V, BR |

| DS3150 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3.3V, DS3/E3/STS-1 Line Interface Unit |

| DS3150DK | 功能描述:网络开发工具 DS3150 Dev Kit RoHS:否 制造商:Rabbit Semiconductor 产品:Development Kits 类型:Ethernet to Wi-Fi Bridges 工具用于评估:RCM6600W 数据速率:20 Mbps, 40 Mbps 接口类型:802.11 b/g, Ethernet 工作电源电压:3.3 V |

| DS3150G | 功能描述:IC LIU T3/E3/STS-1 49-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

| DS3150GN | 功能描述:IC LIU T3/E3/STS-1 IND 49-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:25 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:4.5 V ~ 5.5 V 安装类型:通孔 封装/外壳:16-DIP(0.300",7.62mm) 供应商设备封装:16-PDIP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。