参数资料

| 型号: | DS32512N# |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 61/130页 |

| 文件大小: | 0K |

| 描述: | IC LIU DS3/E3/STS-1 484-BGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 60 |

| 类型: | 线路接口装置(LIU) |

| 规程: | DS3 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 484-BGA |

| 供应商设备封装: | 484-BGA(23x23) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页当前第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页

DS32506/DS32508/DS32512

36 of 130

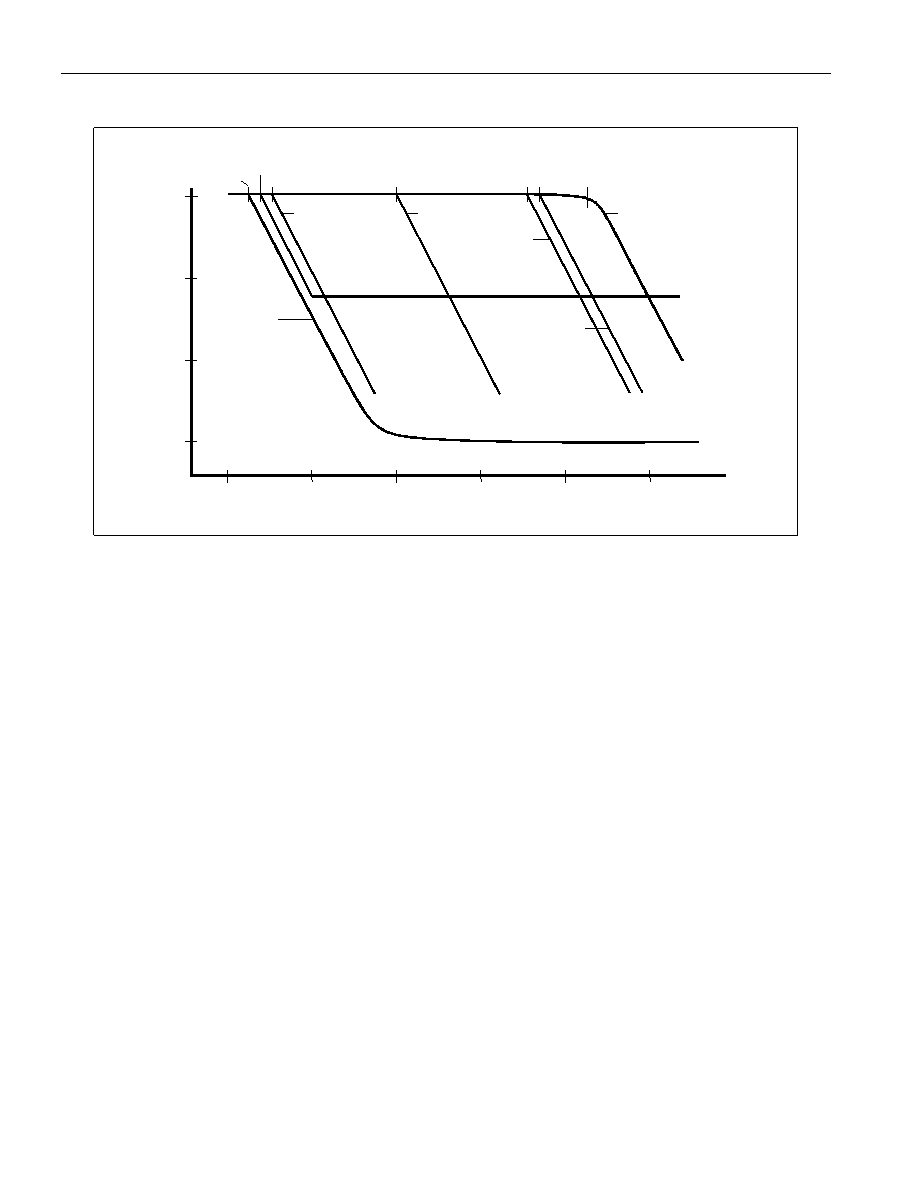

Figure 8-7. Jitter Attenuation/Jitter Transfer

10

100

1k

10k

100k

1M

21.7 Hz (DS3)

16.7 Hz (E3)

25.2 Hz (STS -1)

1k

-30

-20

-10

E3 [TBR24 (1997)]

FREQUENCY (Hz)

JI

TT

E

R

A

TT

E

N

U

A

TI

O

N

(d

B

)

0

DS3 [GR - 499 (1995)]

CATEGORY I

DS325xx TYPICAL

RECEIVER JITTER

TRANSFER WITH

JITTER ATTENUATOR

DISABLED

>150k

DS325xx

DS3/E3/STS-1

MINIMUM

JITTER

ATTENUATION

WITH JITTER

ATTENUATOR

ENABLED

40Hz

DS3 [GR - 253 (1999)]

CATEGORY I

27Hz

STS- 1 [GR - 253 (1999)]

CATEGORY II

40k 59.6k

DS3 [GR - 499 (1999)]

CATEGORY II

8.5 BERT

Each LIU port has a built-in bit error-rate tester (BERT). The BERT is a software-programmable test-pattern

generator and monitor capable of meeting most error performance requirements for digital transmission equipment.

It can generate and synchronize to pseudo-random patterns with a generation polynomial of the form x

n + xy + 1,

(where n and y can take on values from 1 to 32 with y < n) and to repetitive patterns of any length up to 32 bits.

The pattern generator generates the programmable test pattern, and inserts the test pattern into the data stream.

The pattern detector extracts the test pattern from the receive data stream and monitors it. Figure 2-1 shows the

location of the BERT Block within the DS325xx devices.

8.5.1 Configuration and Monitoring

The pattern detector is always enabled. The pattern generator is enabled by setting the PORT.CR3:BERTE

configuration bit. When the BERT is enabled and PORT.CR3:BERTD=0, the pattern is transmitted and received in

the line direction, i.e. the pattern generator is the data source for the transmitter, and the receiver is the data source

for the pattern detector. When the BERT is enabled and PORT.CR3:BERTD=1, the pattern is transmitted and

received in the system direction, i.e. the pattern generator is the data source for the RPOS/RDAT and RNEG/RLCV

The I/O of the BERT are binary (NRZ) format. Thus while the BERT is enabled, both PORT.CR2:RBIN and

PORT.CR2:TBIN must be set to 1 for proper operation. In addition, while transmitting/receiving BERT patterns in

the system direction (PORT.CR3:BERTD = 1), the neighboring framer or mapper component must also be

configured for binary interface mode to match the LIU. If the LIU interface is normally bipolar, the interface can be

changed back to bipolar mode when the system is done using the BERT function (PORT.CR3:BERTE = 0).

The following tables show how to configure the BERT to send and receive common patterns.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1228AEEP+T | IC ADC 12BIT 300KSPS 20-QSOP |

| VI-26W-IU-F4 | CONVERTER MOD DC/DC 5.5V 200W |

| DS32512+ | IC LIU DS3/E3/STS-1 484-BGA |

| VI-26W-IU-F2 | CONVERTER MOD DC/DC 5.5V 200W |

| M83723/71W1020Y | CONN RCPT 2POS WALL MT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS32512N# | 功能描述:网络控制器与处理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS32512N+ | 功能描述:网络控制器与处理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS32512NA2 | 制造商:Maxim Integrated Products 功能描述:DS32512 X12 DS3/E3 LIU REVA2 IND - Rail/Tube |

| DS32512NW | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS32512W | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。