- 您现在的位置:买卖IC网 > PDF目录15530 > EVAL-ADUC7039QSPZ (Analog Devices Inc)BOARD EVAL FOR ADUC7039 PDF资料下载

参数资料

| 型号: | EVAL-ADUC7039QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 17/92页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADUC7039 |

| 设计资源: | ADuC7039QSPZ Gerber Files EVAL-ADuC7039 Schematic & Brd Outline |

| 标准包装: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 类型: | MCU |

| 适用于相关产品: | ADuC7039 |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADuC7039

Data Sheet

Rev. D | Page 24 of 92

FLASH/EE MEMORY RELIABILITY

The Flash/EE memory array on the part is fully qualified for

two key Flash/EE memory characteristics: Flash/EE memory

cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to be

cycled through many program, read, and erase cycles. A single

endurance cycle is composed of four independent, sequential

events, defined as

Initial page erase sequence.

Read/verify sequence.

Byte program sequence.

Second read/verify sequence.

In reliability qualification, every half-word (16-bit wide) loca-

tion of the three pages (top, middle, and bottom) in the Flash/EE

memory is cycled 10,000 times from 0x0000 to 0xFFFF. As

indicated in Table 1, the Flash/EE memory endurance qualifi-

cation of the part is carried out in accordance with the JEDEC

Retention Lifetime Specification A117. The results allow the

specification of a minimum endurance figure over supply and

temperature of 10,000 cycles.

Retention quantifies the ability of the Flash/EE memory to

retain its programmed data over time. The part is qualified in

accordance with the formal JEDEC Retention Lifetime Specifi-

cation A117 at a specific junction temperature (TJ = 85°C) as

indicated in Table 1. This means that the Flash/EE memory

is guaranteed to retain its data for its fully specified retention

lifetime every time the Flash/EE memory is reprogrammed.

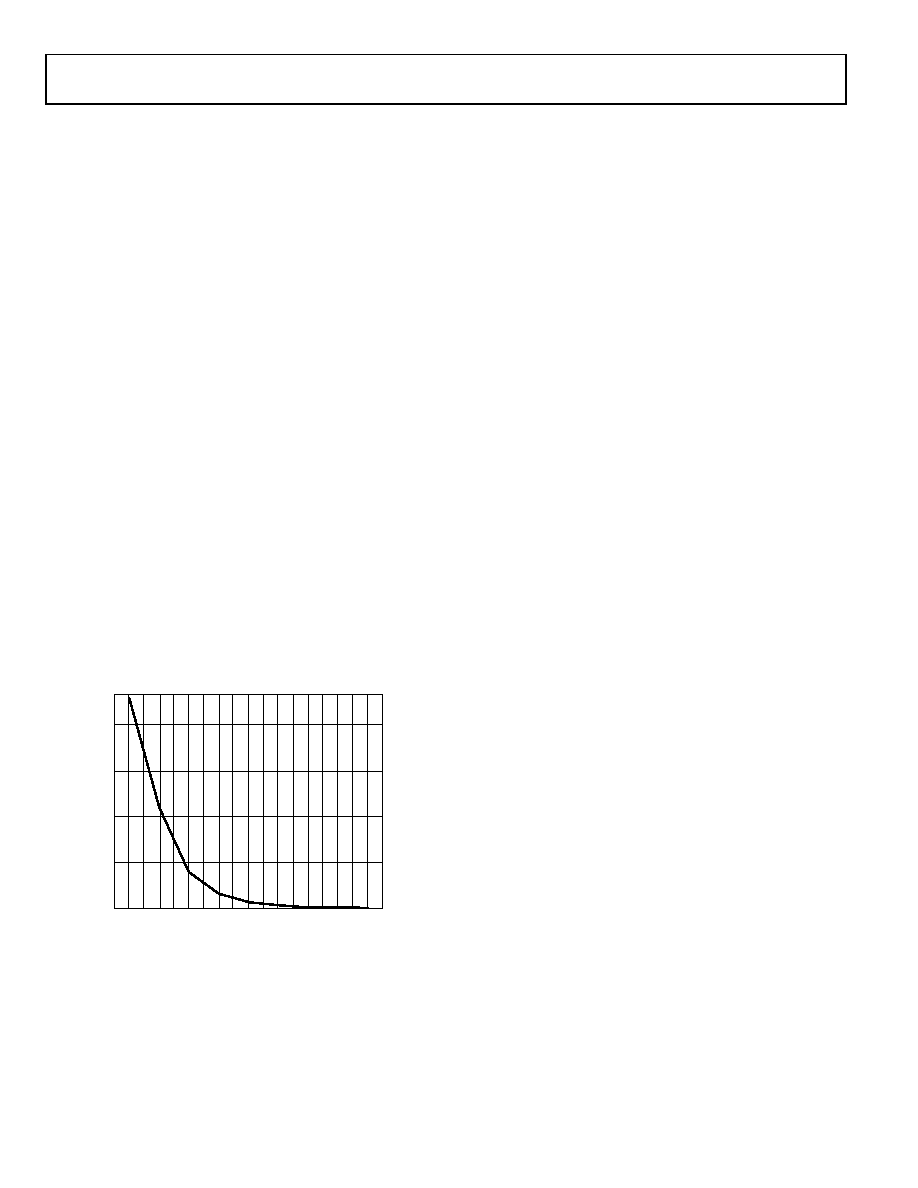

Also, note that retention lifetime, based on an activation energy

Figure 8. Flash/EE Memory Data Retention

ADuC7039 KERNEL

The ADuC7039 features an on-chip kernel resident in the

top 2 kB of the Flash/EE code space. After any reset event,

this kernel calculates its own checksum and compares it to the

checksum programmed during production test, to ensure that

the kernel does not contain any error. If an error occurs, the

SYSCHK register contains its default value and user mode is

entered. In normal circumstances, the checksum is written to

the SYSCHK MMR.

System Kernel Checksum

Name:

SYSCHK

Address:

0xFFFF0244

Default Value: 0x00000000 (updated by kernel at power-on)

Access:

Read/write

Function:

At power-on, this 32-bit register holds the

kernel checksum.

The kernel then copies the factory calibrated data from the

manufacturing data space into the various on-chip peripherals.

The peripherals calibrated by the kernel are as follows:

Precision oscillator

Low power oscillator

REG_AVDD/REG_DVDD

Voltage reference

Current ADC (offset and gain)

Voltage/temperature ADC (offset and gain)

Processor registers and user registers that can be modified

by the kernel and differ from their POR default values are as

follows:

R0 to R15

GP0CON

SYSCHK

FEEADR/FEEDAT/FEECON/FEESIG

HVDAT/HVCON

HVCFG

T2LD

The ADuC7039 also features an on-chip LIN downloader.

A flow chart of the execution of the kernel is shown in Figure 9.

The current revision of the kernel can be derived from R5, as

described in Table 66.

After any reset, the watchdog timer is disabled once the kernel

code is exited. For the duration of the kernel execution, the

watchdog timer is active with a timeout period of 500 ms. This

ensures that if an error occurs in the kernel, the ADuC7039

automatically resets. If LIN download mode is entered, the

watchdog is periodically refreshed.

0

150

300

450

600

30

40

55

70

85

100

125

135

150

RE

T

E

NT

IO

N

(

Y

ears)

JUNCTION TEMPERATURE (°C)

08463-

009

相关PDF资料 |

PDF描述 |

|---|---|

| EYM15DRSH | CONN EDGECARD 30POS DIP .156 SLD |

| AIUR-06-102K | INDUCTOR POWER 1000UH 10% T/H |

| V300C3V3C50B2 | CONVERTER MOD DC/DC 3.3V 50W |

| EGM15DRSH | CONN EDGECARD 30POS DIP .156 SLD |

| EVAL-ADUC7023QSPZ1 | BOARD EVAL FOR ADUC7023 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7060QSPZ | 功能描述:KIT DEV QUICK START ADUC7060 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:QuickStart™ PLUS 套件 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| EVAL-ADUC7060QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVALADUC7060QSPZU2 | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits) |

| EVAL-ADUC7061MKZ | 功能描述:开发板和工具包 - ARM Quick Start Development System RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V |

| EVAL-ADUC7061MKZ | 制造商:Analog Devices 功能描述:ADUC7061MKZ EvaluationBoard |

发布紧急采购,3分钟左右您将得到回复。