- 您现在的位置:买卖IC网 > PDF目录15530 > EVAL-ADUC7039QSPZ (Analog Devices Inc)BOARD EVAL FOR ADUC7039 PDF资料下载

参数资料

| 型号: | EVAL-ADUC7039QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 6/92页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADUC7039 |

| 设计资源: | ADuC7039QSPZ Gerber Files EVAL-ADuC7039 Schematic & Brd Outline |

| 标准包装: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 类型: | MCU |

| 适用于相关产品: | ADuC7039 |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

ADuC7039

Data Sheet

Rev. D | Page 14 of 92

ARM7 Exceptions

The ARM7 supports five types of exceptions, with a privileged

processing mode associated with each type. The five types of

exceptions are as follows:

Normal interrupt or IRQ. This is provided to service

general-purpose interrupt handling of internal and

external events.

Fast interrupt or FIQ. This is provided to service data

transfer or a communication channel with low latency.

FIQ has priority over IRQ.

Memory abort (prefetch and data).

Attempted execution of an undefined instruction.

Software interrupt (SWI) instruction that can be used

to make a call to an operating system.

Typically, the programmer defines interrupts as IRQ, but

for higher priority interrupts, the programmer can define

interrupts as the FIQ type.

The priority of these exceptions and the vector addresses are

listed in Table 6.

Table 6. Exception Priorities and Vector Addresses

Priority

Exception

Address

1

Hardware reset

0x00

2

Memory abort (data)

0x10

3

FIQ

0x1C

4

IRQ

0x18

5

Memory abort (prefetch)

0x0C

6

Software interrupt1

0x08

6

Undefined instruction1

0x04

1 A software interrupt and an undefined instruction exception have the same

priority and are mutually exclusive.

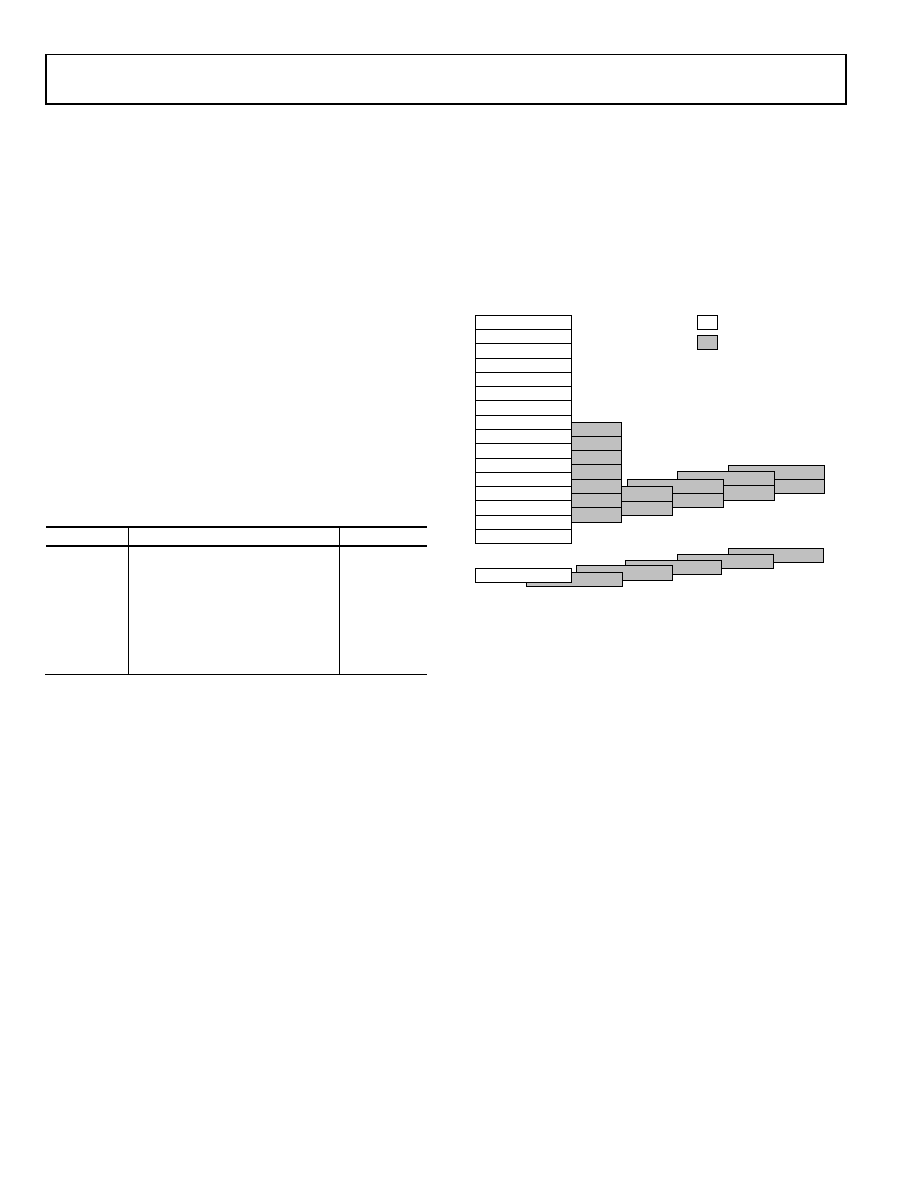

ARM Registers

The ARM7TDMI-S has 16 standard registers. R0 to R12 are

used for data manipulation, R13 is the stack pointer, R14 is the

link register, and R15 is the program counter that indicates the

instruction currently being executed. The link register contains

the address from which the user has branched (if the branch

and link command was used) or the command during which

an exception occurred.

The stack pointer contains the current location of the stack. As

a general rule, on an ARM7TDMI-S, the stack starts at the top

of the available RAM area and descends using the area as

required. A separate stack is defined for each of the exceptions.

The size of each stack is user configurable and is dependent on

the target application. On the ADuC7039, the stack begins at

0x00040FFC and descends. When programming using high

level languages, such as C, it is necessary to ensure that the stack

does not over-flow. This is dependent on the performance of

the compiler that is used.

When an exception occurs, some of the standard registers are

replaced with registers specific to the exception mode. All

exception modes have replacement banked registers for the

stack pointer (R13) and the link register (R14) as represented

in Figure 4. The FIQ mode has more registers (R8 to R12)

supporting faster interrupt processing. With the increased

number of noncritical registers, the interrupt can be processed

without the need to save or restore these registers, thereby

reducing the response time of the interrupt handling process.

More information relative to the programmer’s model and the

ARM7TDMI-S core architecture can be found in ARM7TDMI-S

technical and ARM architecture manuals available directly from

ARM Ltd.

Figure 4. Register Organization

Interrupt Latency

The worst-case latency for an FIQ consists of the longest time

the request can take to pass through the synchronizer, and the

time for the longest instruction to complete (the longest instruc-

tion is an LDM that loads all the registers including the PC),

plus the time for the data abort entry and the time for FIQ

entry. At the end of this time, the ARM7TDMI-S is executing

the instruction at 0x1C (FIQ interrupt vector address). The

maximum total time is 50 processor cycles, or just under 5 μs

in a system using a continuous 10.24 MHz processor clock. The

maximum IRQ latency calculation is similar but must allow for

the fact that FIQ has higher priority and could delay entry into

the IRQ handling routine for an arbitrary length of time. This

time can be reduced to 42 cycles if the LDM command is not

used; some compilers have an option to compile without using

this command. Another option is to run the part in Thumb

mode where this is reduced to 22 cycles.

The minimum latency for FIQ or IRQ interrupts is five cycles.

This consists of the shortest time the request can take through

the synchronizer and the time to enter the exception mode.

Note that the ARM7TDMI-S initially (first instruction) runs

in ARM (32-bit) mode when an exception occurs. The user

can immediately switch from ARM mode to Thumb mode

if required, for example, when executing interrupt service

routines.

USABLE IN USER MODE

SYSTEM MODES ONLY

SPSR_UND

SPSR_IRQ

SPSR_ABT

SPSR_SVC

R8_FIQ

R9_FIQ

R10_FIQ

R11_FIQ

R12_FIQ

R13_FIQ

R14_FIQ

R13_UND

R14_UND

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15 (PC)

R13_IRQ

R14_IRQ

R13_ABT

R14_ABT

R13_SVC

R14_SVC

SPSR_FIQ

CPSR

USER MODE

FIQ

MODE

SVC

MODE

ABORT

MODE

IRQ

MODE

UNDEFINED

MODE

08

463-

004

相关PDF资料 |

PDF描述 |

|---|---|

| EYM15DRSH | CONN EDGECARD 30POS DIP .156 SLD |

| AIUR-06-102K | INDUCTOR POWER 1000UH 10% T/H |

| V300C3V3C50B2 | CONVERTER MOD DC/DC 3.3V 50W |

| EGM15DRSH | CONN EDGECARD 30POS DIP .156 SLD |

| EVAL-ADUC7023QSPZ1 | BOARD EVAL FOR ADUC7023 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7060QSPZ | 功能描述:KIT DEV QUICK START ADUC7060 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:QuickStart™ PLUS 套件 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| EVAL-ADUC7060QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVALADUC7060QSPZU2 | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits) |

| EVAL-ADUC7061MKZ | 功能描述:开发板和工具包 - ARM Quick Start Development System RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V |

| EVAL-ADUC7061MKZ | 制造商:Analog Devices 功能描述:ADUC7061MKZ EvaluationBoard |

发布紧急采购,3分钟左右您将得到回复。