- 您现在的位置:买卖IC网 > PDF目录15530 > EVAL-ADUC7039QSPZ (Analog Devices Inc)BOARD EVAL FOR ADUC7039 PDF资料下载

参数资料

| 型号: | EVAL-ADUC7039QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 85/92页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADUC7039 |

| 设计资源: | ADuC7039QSPZ Gerber Files EVAL-ADuC7039 Schematic & Brd Outline |

| 标准包装: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 类型: | MCU |

| 适用于相关产品: | ADuC7039 |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页当前第85页第86页第87页第88页第89页第90页第91页第92页

ADuC7039

Data Sheet

Rev. D | Page 86 of 92

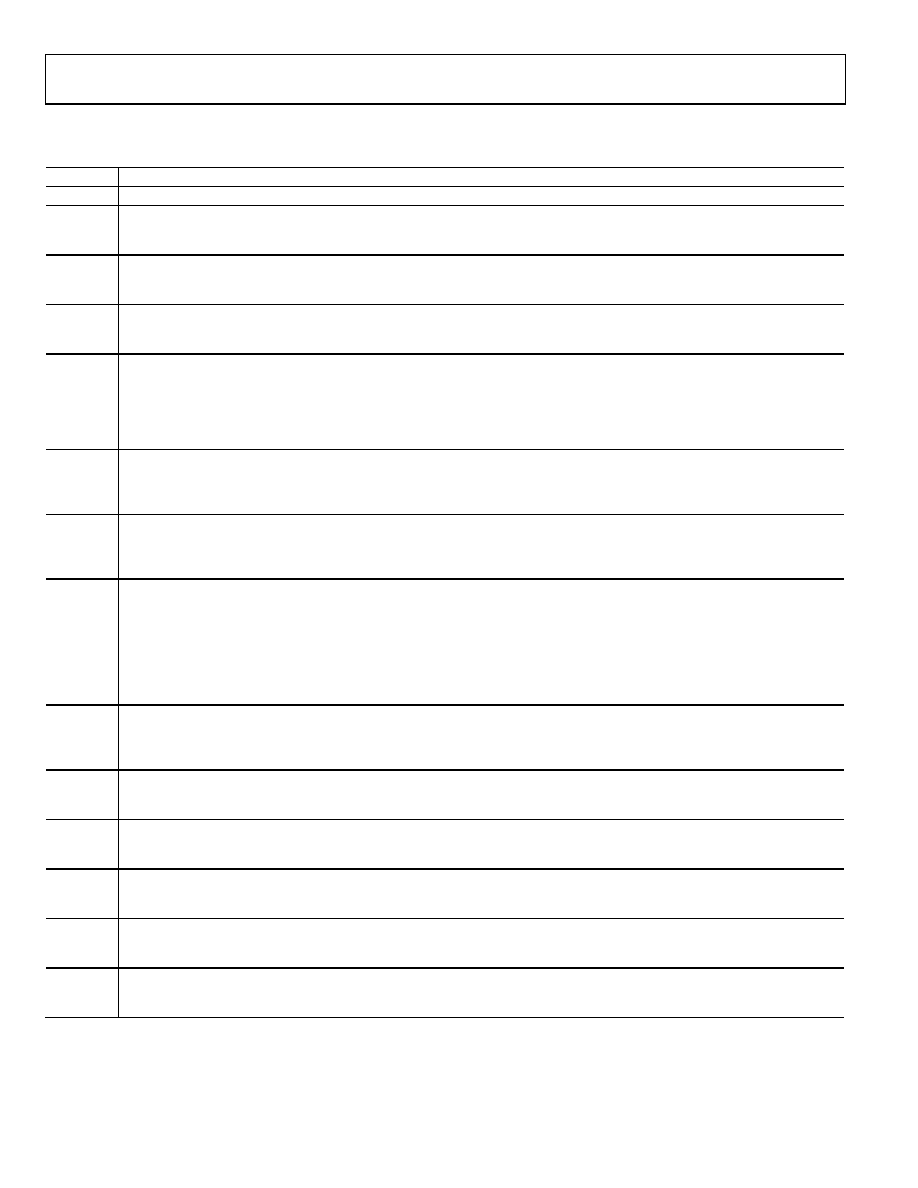

Table 61. LINCON MMR Bit Designations

Bits

Description

15 to 13

Reserved.

12

LIN bypass bit.

This bit is set to 1 by user code to take control of the LIN transceiver alone, for LIN conformance test.

This bit is cleared to 0 by user code to operate in normal mode.

11

LIN enable bit.

This bit is set to 1 by user code to enable the LIN interface.

This bit is cleared to 0 by user code to disable the LIN interface or to reset the interface.

10

UART enable bit.

This bit is set by user code to allow transmission without receiving the frame header, for test purposes.

This bit is cleared by user code for normal mode operation.

9

Timing of sync symbol, Bit 0 (not require in a single slave system).

Ensure that if a second break is transmitted it is recognized as such and not timed as part of the sync symbol. If the start

symbol is more than the number of clock ticks dictated by this bit, the device assumes it is now receiving a break and continues

to count the low cycle to see if the break meets the minimum time required for a break as defined in the LINBK MMR.

Set by the user. The first bit of the sync symbol must be less than 750 core clocks (73 s).

This bit is cleared by the user to disable this functionality.

8

Send checksum.

This bit is set by the user to transmit the checksum automatically. This bit must be set after the last data byte to transmit what

is written in LINDAT and after the transmit ready bit is set.

This bit is cleared automatically by hardware when the checksum is sent.

7

Checksum calculation.

This bit is set by the user to calculate automatically a classic checksum (PID excluded).

This bit is cleared by the user to calculate an enhanced checksum (PID included).

Modifying the value of this bit during communication, for example after receiving a PID, resets the checksum.

6

Collision detect and transmit complete interrupt mask.

This bit is set by the user to disable the collision detect and transmit complete interrupt.

This bit is cleared by the user to enable the collision detect and transmit complete interrupt.

When the interrupt is enabled, all occurrences of collision detected causes an interrupt to occur and the collision status bit to

be asserted, regardless of the state of the transmit finished bit. When masking is enabled, once the transmit is finished,

asserted occurrences of collision detected are masked and do not cause an interrupt to occur or the collision detected status

bit to be set. Even if this masking bit has been set by the user if transmit finished has not been asserted by the device, collisions

cause an interrupt to occur and the collision detected status bit to be set.

5

Negative edge maximum error interrupt mask.

This bit is set by the user to disable the negative edge maximum error interrupt.

This bit is cleared by the user to enable the negative edge maximum error interrupt. An interrupt is generated if the negative

edge counter counts more than 57 edges in a frame.

4

Collision detect interrupt mask.

This bit is set by the user to disable the collision detect interrupt.

This bit is cleared by the user to enable the collision detect interrupt.

3

Break received interrupt mask.

This bit is set by the user to disable the break symbol receive interrupt.

This bit is cleared by the user to enable the break symbol receive interrupt.

2

Transmit complete interrupt mask.

This bit is set by the user to disable the transmit complete interrupt.

This bit is cleared by the user to enable the transmit complete interrupt.

1

Transmit ready interrupt mask.

This bit is set by the user to disable the transmit ready interrupt. Set automatically when LINCON[8] is set.

This bit is cleared by the user to enable the transmit ready interrupt.

0

Receive/transmit mode.

This bit is set by user code to transmit data bytes after decoding the PID.

This bit is cleared automatically when a break symbol is received.

相关PDF资料 |

PDF描述 |

|---|---|

| EYM15DRSH | CONN EDGECARD 30POS DIP .156 SLD |

| AIUR-06-102K | INDUCTOR POWER 1000UH 10% T/H |

| V300C3V3C50B2 | CONVERTER MOD DC/DC 3.3V 50W |

| EGM15DRSH | CONN EDGECARD 30POS DIP .156 SLD |

| EVAL-ADUC7023QSPZ1 | BOARD EVAL FOR ADUC7023 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7060QSPZ | 功能描述:KIT DEV QUICK START ADUC7060 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:QuickStart™ PLUS 套件 产品培训模块:Blackfin® Processor Core Architecture Overview Blackfin® Device Drivers Blackfin® Optimizations for Performance and Power Consumption Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA |

| EVAL-ADUC7060QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVALADUC7060QSPZU2 | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits) |

| EVAL-ADUC7061MKZ | 功能描述:开发板和工具包 - ARM Quick Start Development System RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V |

| EVAL-ADUC7061MKZ | 制造商:Analog Devices 功能描述:ADUC7061MKZ EvaluationBoard |

发布紧急采购,3分钟左右您将得到回复。