- 您现在的位置:买卖IC网 > Datasheet目录324 > EVAL-ADUC7060QSPZ (Analog Devices Inc)KIT DEV QUICK START ADUC7060 Datasheet资料下载

参数资料

| 型号: | EVAL-ADUC7060QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 31/100页 |

| 文件大小: | 0K |

| 描述: | KIT DEV QUICK START ADUC7060 |

| 产品变化通告: | ADuC7060/1 Idd Specification Change 01/Feb/2010 |

| 设计资源: | ADUC7060 Gerber Files EVAL-ADuC7060 schematic |

| 标准包装: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 类型: | MCU |

| 适用于相关产品: | ADuC7060 |

| 所含物品: | 评估板、电源、缆线、软件、仿真器和说明文档 |

| 其它名称: | Q5189809 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

�� �

�

�

�ADuC7060�

�Power� and� Clock� Control� Registers�

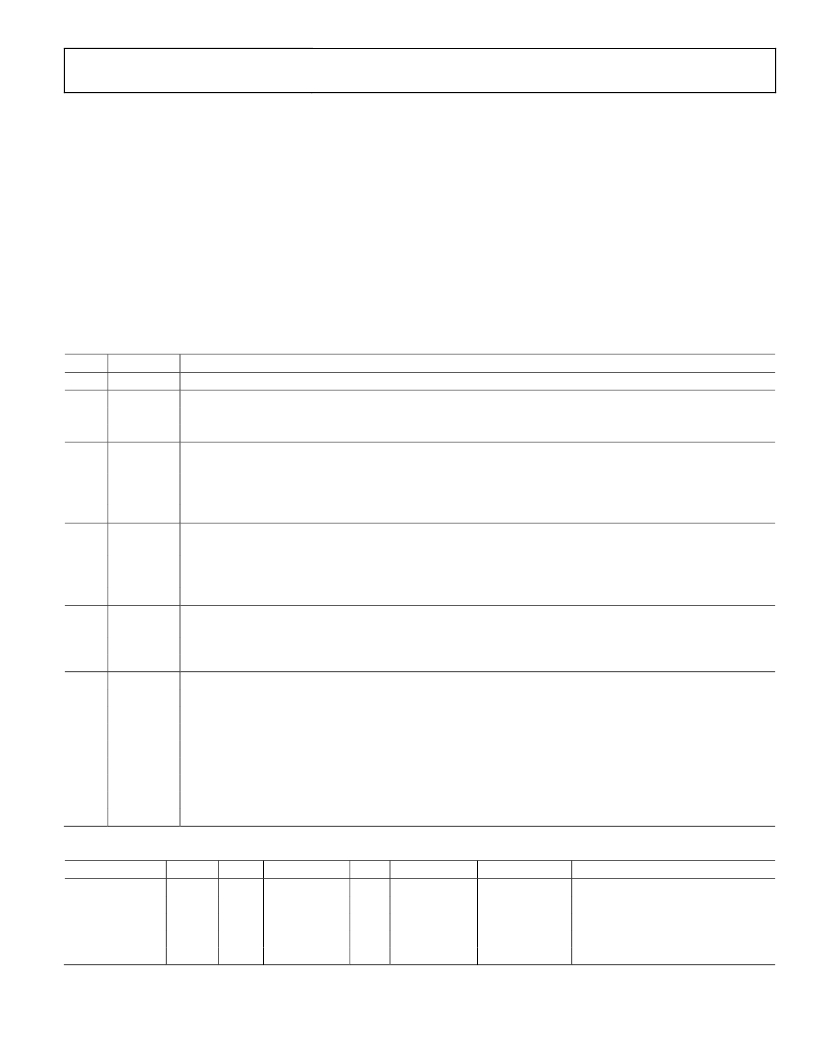

�Name:�

�POWCON0�

�Name:�

�Address:�

�Default� value:�

�Access:�

�Function:�

�POWKEY1�

�0xFFFF0404�

�0xXXXX�

�Write�

�When� writing� to� POWCON0,� the� value� of�

�Address:�

�Default� value:�

�Access:�

�Function:�

�0xFFFF0408�

�0x7B�

�Read� and� write�

�This� register� controls� the� clock� divide� bits�

�controlling� the� CPU� clock� (HCLK).�

�0x01� must� be� written� to� this� register� in� the�

�instruction� immediately� before� writing� to�

�POWCON0.�

�Table� 30.� POWCON0� MMR� Bit� Designations�

�Bit�

�7�

�6�

�5�

�4�

�3�

�2� to� 0�

�Name�

�Reserved�

�XPD�

�PLLPD�

�PPD�

�COREPD�

�CD[2:0]�

�Description�

�This� bit� must� always� be� set� to� 0.�

�XTAL� power-down.�

�Cleared� by� user� to� power� down� the� external� crystal� circuitry.�

�Set� by� user� to� enable� the� external� crystal� circuitry.�

�PLL� power-down.� Timer� peripherals� power� down� if� driven� from� the� PLL� output� clock.� Timers� driven� from� an� active�

�clock� source� remain� in� normal� power� mode.�

�This� bit� is� cleared� to� 0� to� power� down� the� PLL.� The� PLL� cannot� be� powered� down� if� either� the� core� or� peripherals� are�

�enabled;� Bit� 3,� Bit� 4,� and� Bit� 5� must� be� cleared� simultaneously.�

�Set� by� default,� and� set� by� hardware� on� a� wake-up� event.�

�Peripherals� power-down.� The� peripherals� that� are� powered� down� by� this� bit� are� as� follows:�

�SRAM,� Flash/EE� memory� and� GPIO� interfaces,� and� SPI/I� 2� C� and� UART� serial� ports.�

�Cleared� to� power� down� the� peripherals.� The� peripherals� cannot� be� powered� down� if� the� core� is� enabled;� Bit� 3� and�

�Bit� 4� must� be� cleared� simultaneously.�

�Set� by� default,� and/or� by� hardware,� on� a� wake-up� event.� Wake-up� timer� (Timer1)� can� remain� active.�

�Core� power-down.� If� user� code� powers� down� the� MCU,� include� a� dummy� MCU� cycle� after� the� power-down�

�command� is� written� to� POWCON0.�

�Cleared� to� power� down� the� ARM� core.�

�Set� by� default� and� set� by� hardware� on� a� wake-up� event.�

�Core� clock� depends� on� CD� setting:�

�[000]� =� 10.24� MHz�

�[001]� =� 5.12� MHz�

�[010]� =� 2.56� MHz�

�[011]� =� 1.28� MHz� [default� value]�

�[100]� =� 640� kHz�

�[101]� =� 320� kHz�

�[110]� =� 160� kHz�

�[111]� =� 80� kHz�

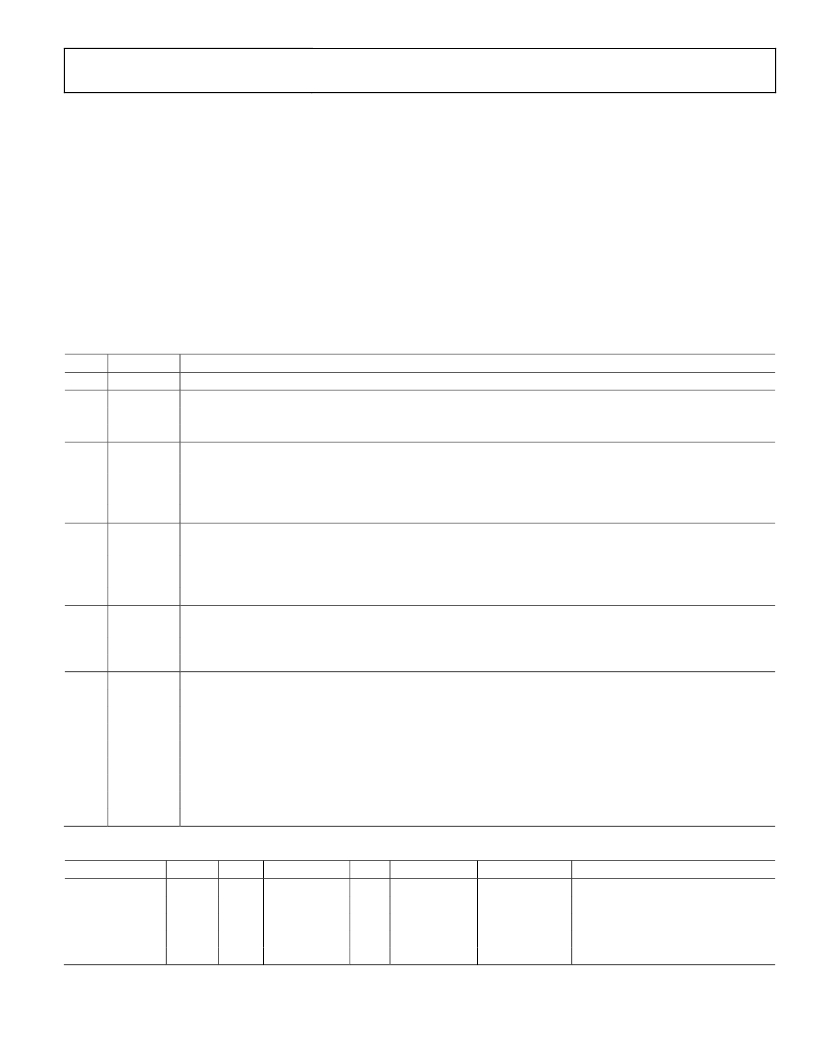

�Table� 31.� ADuC7060� Power� Saving� Modes�

�POWCON0[6:3]�

�1111�

�1110�

�1100�

�Mode�

�Active�

�Pause�

�Nap�

�Core�

�Yes�

�Peripherals�

�Yes�

�Yes�

�PLL�

�Yes�

�Yes�

�Yes�

�XTAL/T2/T3�

�Yes�

�Yes�

�Yes�

�IRQ0� to� IRQ3�

�Yes�

�Yes�

�Yes�

�Start-Up/Power-On� Time�

�130� ms� at� CD� =� 0�

�4.8� μs� at� CD� =� 0;� 660� μs� at� CD� =� 7�

�4.8� μs� at� CD� =� 0;� 660� μs� at� CD� =� 7�

�1000�

�0000�

�Sleep�

�Stop�

�Yes�

�Yes�

�Yes�

�66� μs� at� CD� =� 0;� 900� μs� at� CD� =� 7�

�66� μs� at� CD� =� 0;� 900� μs� at� CD� =� 7�

�Rev.� 0� |� Page� 31� of� 100�

�相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-ADUC845QSPZ | KIT DEV QUICK START ADUC845 |

| EVAL-ADUM3070EBZ | BOARD EVAL FOR ADUM3070 |

| EVAL-SDP-CB1Z | BOARD EVALUATION FOR SDP-CB1 |

| EVB51JM128 | BOARD EVAL FOR MCF51JM128 MCU |

| EVBQE128 | BOARD EVAL FLEXIS QE128 FAMILY |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7060QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVALADUC7060QSPZU2 | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits) |

| EVAL-ADUC7061MKZ | 功能描述:开发板和工具包 - ARM Quick Start Development System RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V |

| EVAL-ADUC7061MKZ | 制造商:Analog Devices 功能描述:ADUC7061MKZ EvaluationBoard |

| EVAL-ADUC7061MKZU2 | 制造商:Analog Devices 功能描述:PN may be NE CE 制造商:Analog Devices 功能描述:EVALUATION CONTROL BOARD - Boxed Product (Development Kits) |

发布紧急采购,3分钟左右您将得到回复。