- 您现在的位置:买卖IC网 > Datasheet目录324 > EVAL-ADUC7060QSPZ (Analog Devices Inc)KIT DEV QUICK START ADUC7060 Datasheet资料下载

参数资料

| 型号: | EVAL-ADUC7060QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 51/100页 |

| 文件大小: | 0K |

| 描述: | KIT DEV QUICK START ADUC7060 |

| 产品变化通告: | ADuC7060/1 Idd Specification Change 01/Feb/2010 |

| 设计资源: | ADUC7060 Gerber Files EVAL-ADuC7060 schematic |

| 标准包装: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 类型: | MCU |

| 适用于相关产品: | ADuC7060 |

| 所含物品: | 评估板、电源、缆线、软件、仿真器和说明文档 |

| 其它名称: | Q5189809 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

�� ��

��

��

��ADuC7060�

�DAC� PERIPHERALS�

�DAC�

�The� ADuC7060� incorporates� a� 12-bit� voltage� output� DAC� on-�

�chip.� The� DAC� has� a� rail-to-rail� voltage� output� buffer� capable� of�

�driving� 5� kΩ/100� pF.�

�MMR� INTERFACE�

�The� DAC� is� configurable� through� a� control� register� and� a� data�

�register.�

�DAC0CON� Register�

�The� DAC� has� four� selectable� ranges.�

�Name:�

�DAC0CON�

�?�

�?�

�?�

�?�

�0� V� to� V� REF� (internal� band� gap� 1.2� V� reference)�

�VREF?� to� VREF+�

�ADC5/EXT_REF2IN?� to� ADC4/EXT_REF2IN+�

�0� V� to� AVDD�

�Address:�

�Default� value:�

�Access:�

�0xFFFF0600�

�0x0200�

�Read� and� write�

�The� maximum� signal� range� is� 0� V� to� AVDD.�

�Op� Amp� Mode�

�As� an� option,� the� DAC� can� be� disabled� and� its� output� buffer�

�used� as� an� op� amp.�

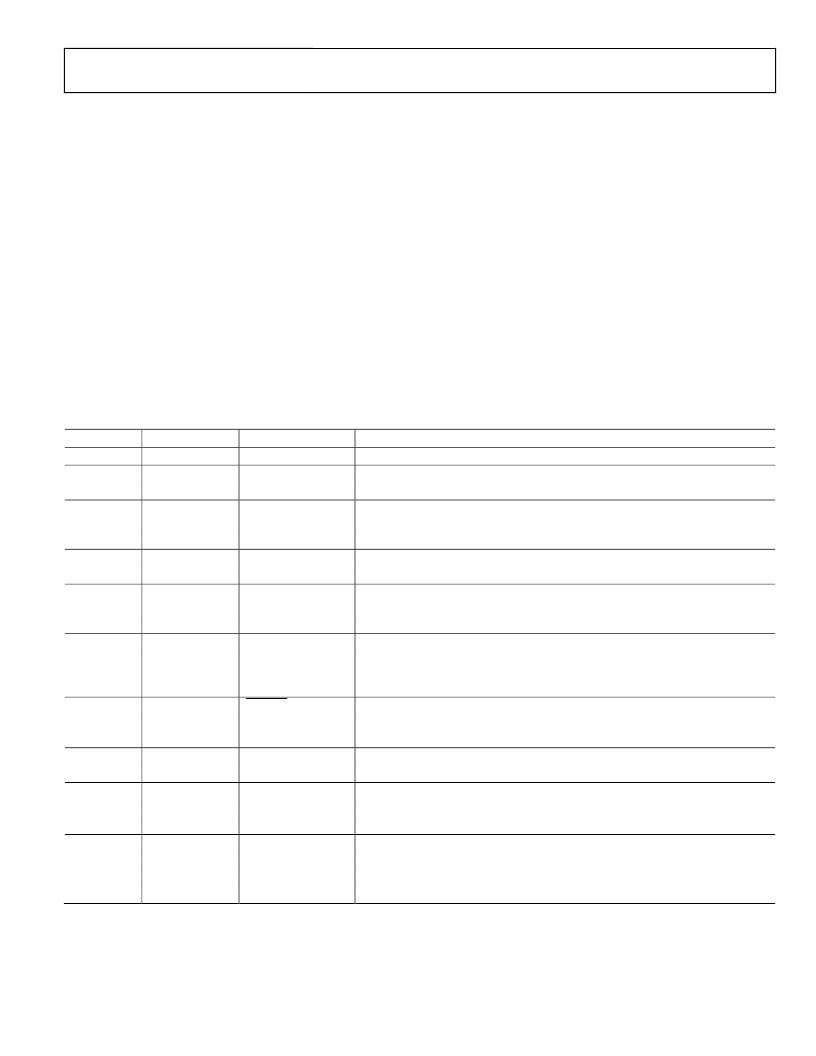

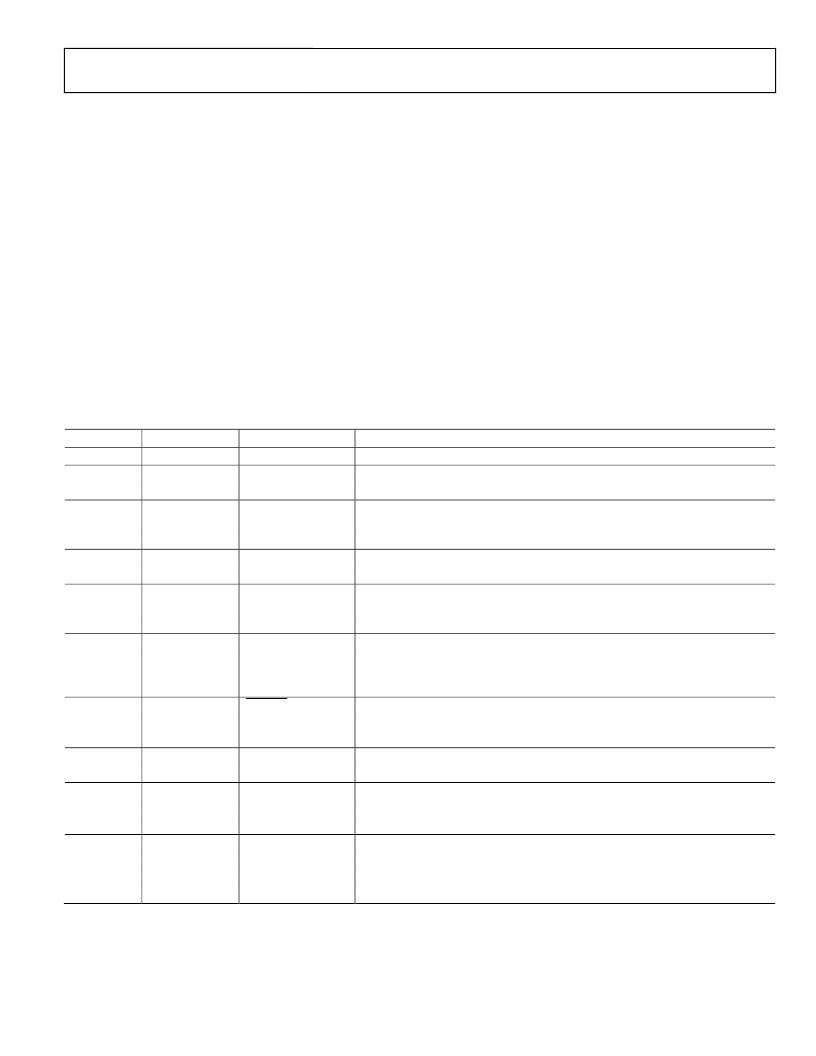

�Table� 61.� DAC0CON� MMR� Bit� Designations�

�Bit�

�15:10�

�9�

�Value�

�Name�

�DACPD�

�Description�

�Reserved.�

�Set� to� 1� to� power� down� DAC� output� (DAC� output� is� tristated).�

�Clear� this� bit� to� enable� the� DAC.�

�8�

�7�

�6�

�5�

�4�

�3�

�2�

�DACBUFLP�

�OPAMP�

�DACBUFBYPASS�

�DACCLK�

�DACCLR�

�DACMODE�

�Rate�

��Mode� and� Op� Amp� Mode� sections� for� further� details� on� electrical� specifications.�

�Clear� this� bit� to� enable� the� DAC� buffer.�

�Set� to� 1� to� place� the� DAC� output� buffer� in� op� amp� mode.�

�Clear� this� bit� to� enable� the� DAC� output� buffer� for� normal� DAC� operation.�

�Set� to� 1� to� bypass� the� output� buffer� and� send� the� DAC� output� directly� to� the�

�output� pin.�

�Clear� this� bit� to� buffer� the� DAC� output.�

�Set� to� 1� to� update� the� DAC� on� the� negative� edge� of� HCLK.�

�Set� to� 0� to� update� the� DAC� on� the� negative� edge� of� Timer1.� This� mode� is� ideally�

�suited� for� waveform� generation� where� the� next� value� in� the� waveform� is� written�

�to� DAC0DAT� at� regular� intervals� of� Timer1.�

�Set� to� 1� for� normal� DAC� operation.�

�Set� to� 0� to� clear� the� DAC� output� and� to� set� DAC0DAT� to� 0.� Writing� to� this� bit� has�

�an� immediate� effect� on� the� DAC� output.�

�Set� to� 1� to� enable� DAC� in� 16-bit� interpolation� mode.�

�Set� to� 0� to� enable� DAC� in� normal� 12-bit� mode.�

�Used� with� interpolation� mode.�

�Set� to� 1� to� configure� the� interpolation� clock� as� UCLK/16.�

�Set� to� 0� to� configure� the� interpolation� clock� as� UCLK/32.�

�1:0�

�11�

�10�

�01�

�00�

�DAC� range� bits�

�0� V� to� AVDD� range.�

�ADC5/EXT_REF2IN?� to� ADC4/EXT_REF2IN+.�

�VREF?� to� VREF+.�

�0� V� to� V� REF� (1.2� V)� range.� Internal� reference� source.�

�Rev.� 0� |� Page� 51� of� 100�

�相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-ADUC845QSPZ | KIT DEV QUICK START ADUC845 |

| EVAL-ADUM3070EBZ | BOARD EVAL FOR ADUM3070 |

| EVAL-SDP-CB1Z | BOARD EVALUATION FOR SDP-CB1 |

| EVB51JM128 | BOARD EVAL FOR MCF51JM128 MCU |

| EVBQE128 | BOARD EVAL FLEXIS QE128 FAMILY |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7060QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVALADUC7060QSPZU2 | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits) |

| EVAL-ADUC7061MKZ | 功能描述:开发板和工具包 - ARM Quick Start Development System RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V |

| EVAL-ADUC7061MKZ | 制造商:Analog Devices 功能描述:ADUC7061MKZ EvaluationBoard |

| EVAL-ADUC7061MKZU2 | 制造商:Analog Devices 功能描述:PN may be NE CE 制造商:Analog Devices 功能描述:EVALUATION CONTROL BOARD - Boxed Product (Development Kits) |

发布紧急采购,3分钟左右您将得到回复。