- 您现在的位置:买卖IC网 > Datasheet目录324 > EVAL-ADUC7060QSPZ (Analog Devices Inc)KIT DEV QUICK START ADUC7060 Datasheet资料下载

参数资料

| 型号: | EVAL-ADUC7060QSPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 43/100页 |

| 文件大小: | 0K |

| 描述: | KIT DEV QUICK START ADUC7060 |

| 产品变化通告: | ADuC7060/1 Idd Specification Change 01/Feb/2010 |

| 设计资源: | ADUC7060 Gerber Files EVAL-ADuC7060 schematic |

| 标准包装: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 类型: | MCU |

| 适用于相关产品: | ADuC7060 |

| 所含物品: | 评估板、电源、缆线、软件、仿真器和说明文档 |

| 其它名称: | Q5189809 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页

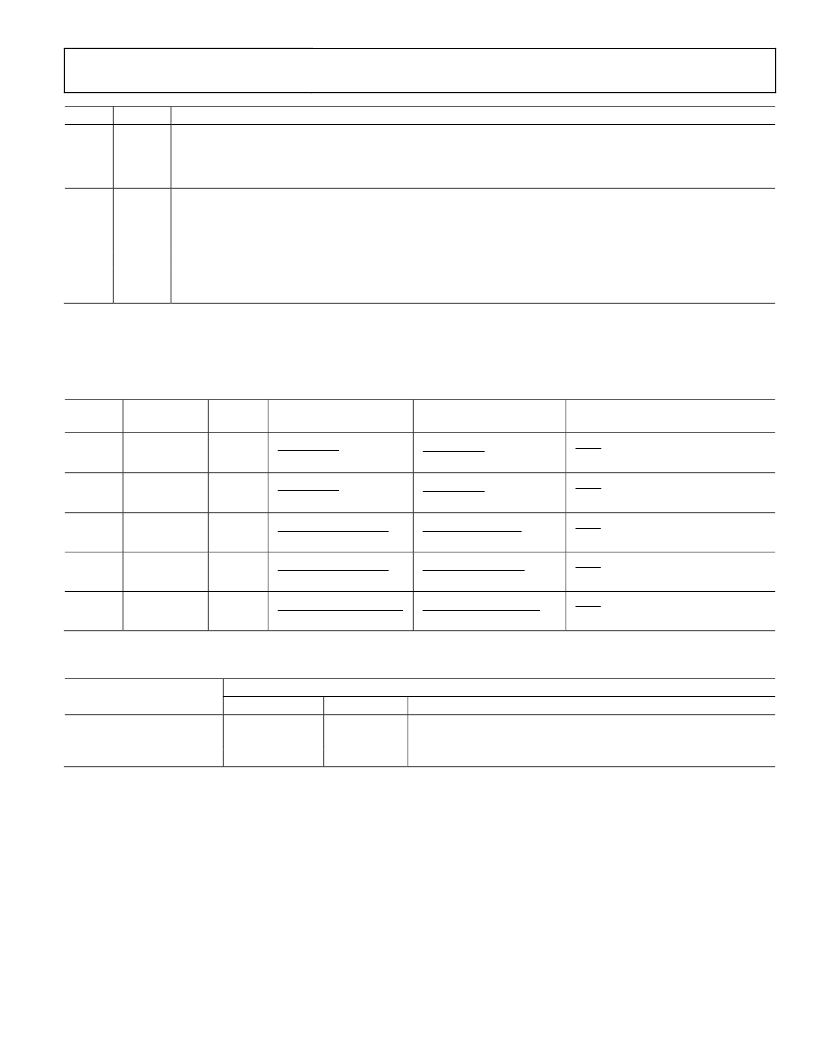

�� �

�

�

�ADuC7060�

�Bit�

�7�

�6� to� 0�

�Name�

�NOTCH2�

�SF[6:0]�

�Description�

�Sinc3� modify.� Set� by� user� to� modify� the� standard� sinc3� frequency� response� to� increase� the� filter� stop� band� rejection� by�

�approximately� 5� dB.� This� is� achieved� by� inserting� a� second� notch� (NOTCH2)� at�

�f� NOTCH2� =� 1.333� � f� NOTCH�

�where� f� NOTCH� is� the� location� of� the� first� notch� in� the� response.�

�Sinc3� decimation� factor� (SF)� 1� .The� value� (SF)� written� in� these� bits� controls� the� oversampling� (decimation� factor)� of� the�

�sinc3� filter.� The� output� rate� from� the� sinc3� filter� is� given� by�

�f� ADC� =� (512,000/([� SF� +1]� � 64))� Hz� 2�

�when� the� chop� bit� (Bit� 15,� chop� enable)� =� 0� and� the� averaging� factor� (AF)� =� 0.� This� is� valid� for� all� SF� values� ≤� 125.�

�For� SF� =� 126,� f� ADC� is� forced� to� 60� Hz.�

�For� SF� =� 127,� f� ADC� is� forced� to� 50� Hz.�

�For� information� on� calculating� the� f� ADC� for� SF� (other� than� 126� and� 127)� and� AF� values,� refer� to� Table� 44.�

�1�

�2�

�Due� to� limitations� on� the� digital� filter� internal� data� path,� there� are� some� limitations� on� the� combinations� of� the� sinc3� decimation� factor� (SF)� and� averaging� factor� (AF)�

�that� can� be� used� to� generate� a� required� ADC� output� rate.� This� restriction� limits� the� minimum� ADC� update� in� normal� power� mode� to� 4� Hz� or� 1� Hz� in� lower� power� mode.�

�In� low� power� mode� and� low� power� plus� mode,� the� ADC� is� driven� directly� by� the� low� power� oscillator� (131� kHz)� and� not� 512� kHz.� All� f� ADC� calculations� should� be� divided�

�by� 4� (approximately).�

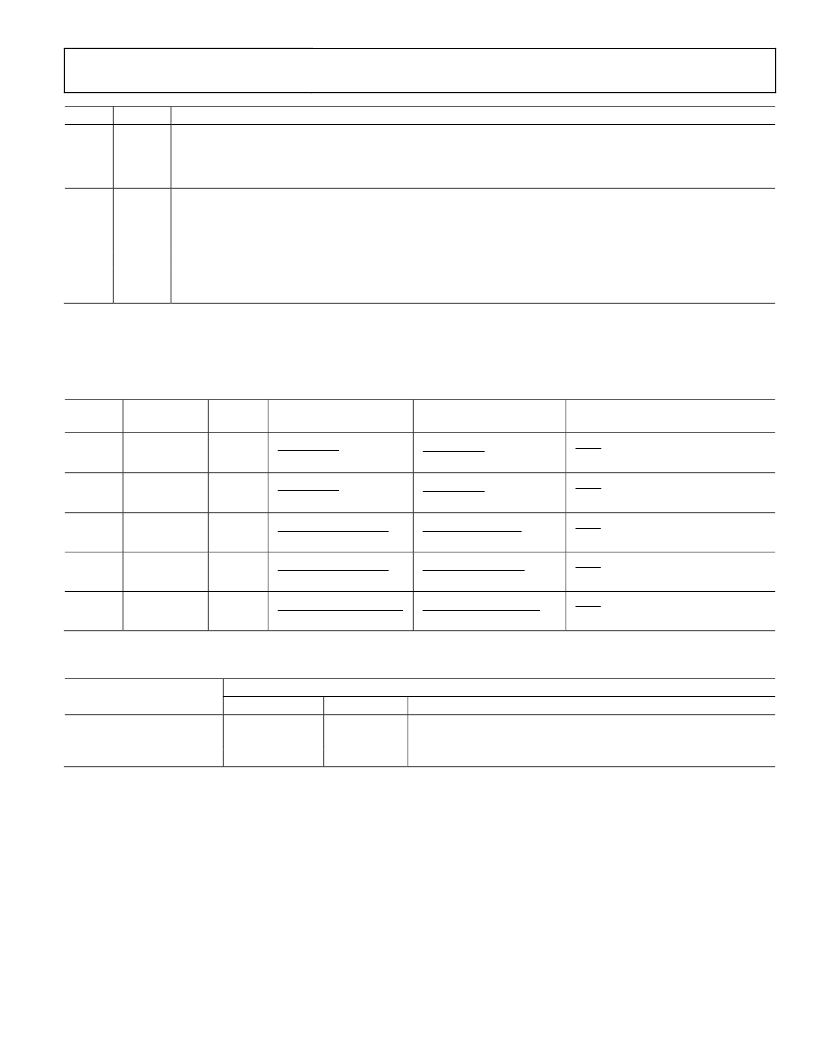

�Table� 44.� ADC� Conversion� Rates� and� Settling� Times�

�Chop�

�Averaging�

�Running�

�Enabled�

�No�

�Factor�

�No�

�Average�

�No�

�f� ADC� Normal� Mode�

�512� ,� 000�

�f� ADC� Low� Power� Mode�

�131� ,� 072�

�t� SETTLING� 1�

�3�

�[� SF� +� 1� ]� � 64�

�[� SF� +� 1� ]� � 64�

�f� ADC�

�No�

�No�

�Yes�

�512� ,� 000�

�131� ,� 072�

�4�

�[� SF� +� 1� ]� � 64�

�[� SF� +� 1� ]� � 64�

�f� ADC�

�No�

�Yes�

�No�

�512� ,� 000�

�131� ,� 072�

�1�

�[� SF� +� 1� ]� � 64� � [� 3� +� AF� ]�

�[� SF� +� 1� ]� � 64� � [� 3� +� AF� ]�

�f� ADC�

�No�

�Yes�

�Yes�

�512� ,� 000�

�131� ,� 072�

�2�

�[� SF� +� 1� ]� � 64� � [� 3� +� AF� ]�

�[� SF� +� 1� ]� � 64� � [� 3� +� AF� ]�

�f� ADC�

�Yes�

�N/A�

�N/A�

�512� ,� 000�

�131� ,� 072�

�2�

�[� SF� +� 1� ]� � 64� � [� 3� +� AF� ]� +� 3�

�[� SF� +� 1� ]� � 64� � [� 3� +� AF� ]� +� 3�

�f� ADC�

�1�

�An� additional� time� of� approximately� 60� μs� per� ADC� is� required� before� the� first� ADC� is� available.�

�Table� 45.� Allowable� Combinations� of� SF� and� AF�

�AF� Range�

�SF�

�0� to� 31�

�32� to� 63�

�64� to� 127�

�0�

�Yes�

�Yes�

�Yes�

�1� to� 7�

�Yes�

�Yes�

�No�

�8� to� 63�

�Yes�

�No�

�No�

�Rev.� 0� |� Page� 43� of� 100�

�相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-ADUC845QSPZ | KIT DEV QUICK START ADUC845 |

| EVAL-ADUM3070EBZ | BOARD EVAL FOR ADUM3070 |

| EVAL-SDP-CB1Z | BOARD EVALUATION FOR SDP-CB1 |

| EVB51JM128 | BOARD EVAL FOR MCF51JM128 MCU |

| EVBQE128 | BOARD EVAL FLEXIS QE128 FAMILY |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-ADUC7060QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVALADUC7060QSPZU2 | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Boxed Product (Development Kits) |

| EVAL-ADUC7061MKZ | 功能描述:开发板和工具包 - ARM Quick Start Development System RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V |

| EVAL-ADUC7061MKZ | 制造商:Analog Devices 功能描述:ADUC7061MKZ EvaluationBoard |

| EVAL-ADUC7061MKZU2 | 制造商:Analog Devices 功能描述:PN may be NE CE 制造商:Analog Devices 功能描述:EVALUATION CONTROL BOARD - Boxed Product (Development Kits) |

发布紧急采购,3分钟左右您将得到回复。