- 您现在的位置:买卖IC网 > PDF目录175496 > HY27SS16561M-FCP (HYNIX SEMICONDUCTOR INC) 16M X 16 FLASH 1.8V PROM, 10000 ns, PBGA63 PDF资料下载

参数资料

| 型号: | HY27SS16561M-FCP |

| 厂商: | HYNIX SEMICONDUCTOR INC |

| 元件分类: | PROM |

| 英文描述: | 16M X 16 FLASH 1.8V PROM, 10000 ns, PBGA63 |

| 封装: | 9 X 11 MM, 1.20 MM HEIGHT, 0.80 MM PITCH, FBGA-63 |

| 文件页数: | 10/44页 |

| 文件大小: | 644K |

| 代理商: | HY27SS16561M-FCP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

Rev 0.4 / Jun. 2004

18

Preliminary

HY27SS(08/16)561M Series

HY27US(08/16)561M Series

256Mbit (32Mx8bit / 16Mx16bit) NAND Flash

Copy Back Program

The Copy Back Program operation is used to copy the data stored in one page and reprogram it in another page.

The Copy Back Program operation does not require external memory and so the operation is faster and more efficient

because the reading and loading cycles are not required. The operation is particularly useful when a portion of a block

is updated and the rest of the block needs to be copied to the newly assigned block.

If the Copy Back Program operation fails an error is signalled in the Status Register. However as the standard external

ECC cannot be used with the Copy Back operation bit error due to charge loss cannot be detected. For this reason it is

recommended to limit the number of Copy Back operations on the same data and or to improve the performance of

the ECC.

The Copy Back Program operation requires three steps:

- 1. The source page must be read using the Read A command (one bus write cycle to setup the command and then

3 bus cycles to input the source page address). This operation copies all 264 Words/ 528 Bytes from the page into the

Page Buffer.

- 2. When the device returns to the ready state (Ready/Busy High), the second bus write cycle of the command is

given with the 3 bus cycles to input the target page address.

A24 must be the same for the Source and Target Pages.

- 3. Then the confirm command is issued to start the P/E/R Controller.

After a Copy Back Program operation, a partial page program is not allowed in the target page until the block has been

erased.

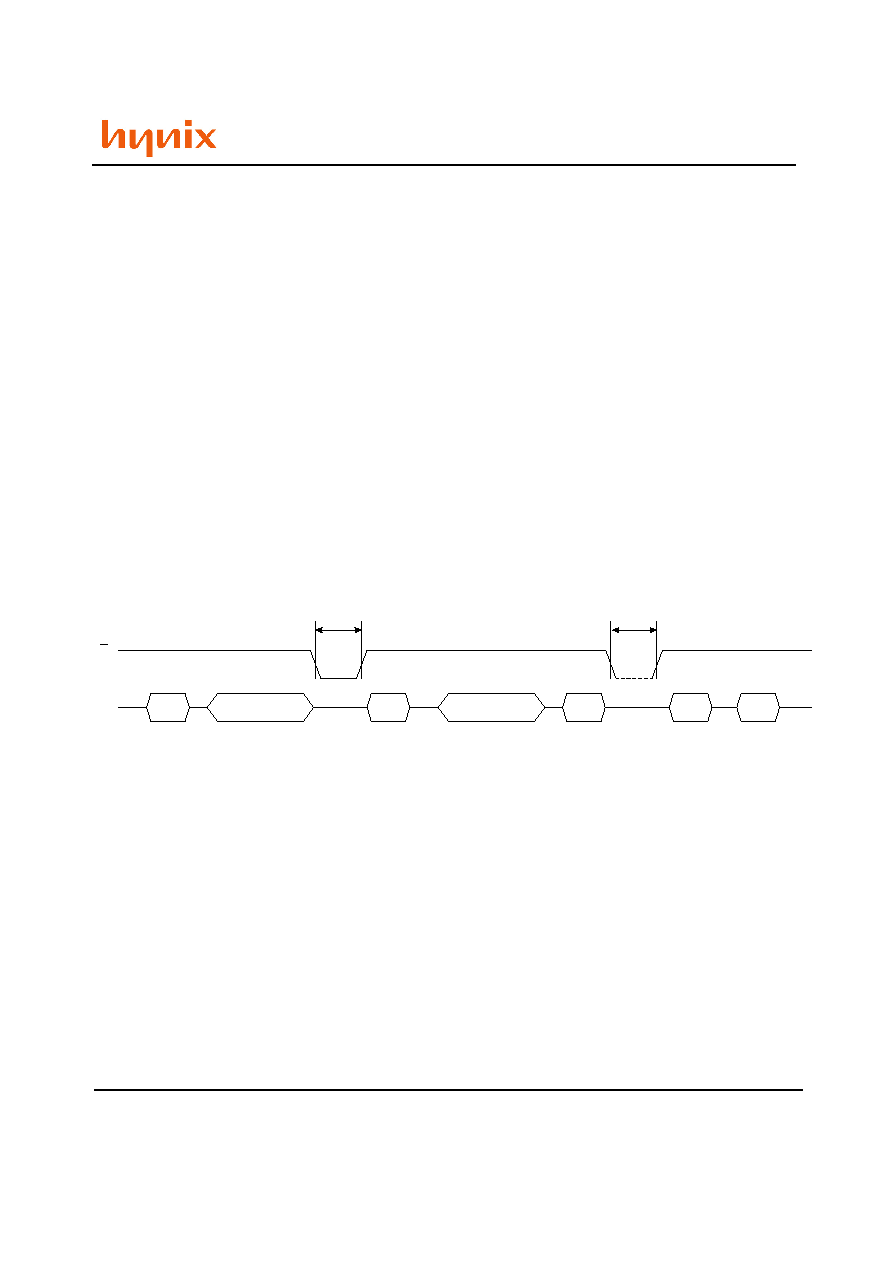

See Figure 15 for an example of the Copy Back operation.

Block Erase

Erase operations are done one block at a time. An erase operation sets all of the bits in the addressed block to '1'. All

previous data in the block is lost. An erase operation consists of three steps (refer to Figure 17):

1. One bus cycle is required to setup the Block Erase command.

2. Only two bus cycles for 256Mb devices are required to input the block address. The first cycle (A0 to A7) is not

required as only addresses A14 to A24 (highest address depends on device density) are valid, A9 to A13 are ignored.

3. One bus cycle is required to issue the confirm command to start the P/E/R Controller.

Once the erase operation has completed the Status Register can be checked for errors.

Figure 15. Copy Back Operation

Source

Address Inputs

I/O

00h

Copy Back

Code

Target

Address Inputs

8Ah

10h

70h

Read

Code

Read Status Register

SR0

Busy

tBLBH2

(Program Busy time)

tBLBH1

(Read Busy time)

RB

相关PDF资料 |

PDF描述 |

|---|---|

| HY27UG084G2M-UPIP | 512M X 8 FLASH 3.3V PROM, 30 ns, PBGA52 |

| HY27UG084GDM-TPIS | 512M X 8 FLASH 3.3V PROM, 30 ns, PDSO48 |

| HY29F040AC-55E | 512K X 8 FLASH 5V PROM, 55 ns, PQCC32 |

| HY5116160CTC-70 | 1M X 16 FAST PAGE DRAM, 70 ns, PDSO44 |

| HY5116404BSLR-60 | 4M X 4 EDO DRAM, 60 ns, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HY27SS561M | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:256Mbit (32Mx8bit / 16Mx16bit) NAND Flash |

| HY27SSXXX | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:512Mbit (64Mx8bit / 32Mx16bit) NAND Flash |

| HY27UA081G1M | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:1Gbit (128Mx8bit / 64Mx16bit) NAND Flash Memory |

| HY27UA161G1M | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:1Gbit (128Mx8bit / 64Mx16bit) NAND Flash Memory |

| HY27UA1G1M | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:1Gbit (128Mx8bit / 64Mx16bit) NAND Flash Memory |

发布紧急采购,3分钟左右您将得到回复。