- 您现在的位置:买卖IC网 > PDF目录175506 > I5104XY (WINBOND ELECTRONICS CORP) 262.2 SEC, SPEECH SYNTHESIZER WITH RCDG, UUC25 PDF资料下载

参数资料

| 型号: | I5104XY |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | 音频合成 |

| 英文描述: | 262.2 SEC, SPEECH SYNTHESIZER WITH RCDG, UUC25 |

| 封装: | DIE-25 |

| 文件页数: | 61/87页 |

| 文件大小: | 616K |

| 代理商: | I5104XY |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页当前第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

65

8393B-MCU Wireless-02/13

ATmega256/128/64RFR2

Value

Name

Description

5

NO_ACK

No acknowledgement frames were received

during all retry attempts

7

INVALID

Entering TX_ARET mode sets

TRAC_STATUS = 7

Note that if no ACK is expected (according to the content of the received frame in the

Frame Buffer), the radio transceiver issues a TRX24_TX_END interrupt directly after

the frame transmission has been completed. The value of the bits TRAC_STATUS of

register TRX_STATE is set to SUCCESS.

A value of MAX_CSMA_RETRIES = 7 initiates an immediate TX_ARET transaction

without performing CSMA-CA. This is required to support slotted acknowledgement

operation. Further the value MAX_FRAME_RETRIES is ignored and the TX_ARET

transaction is performed only once.

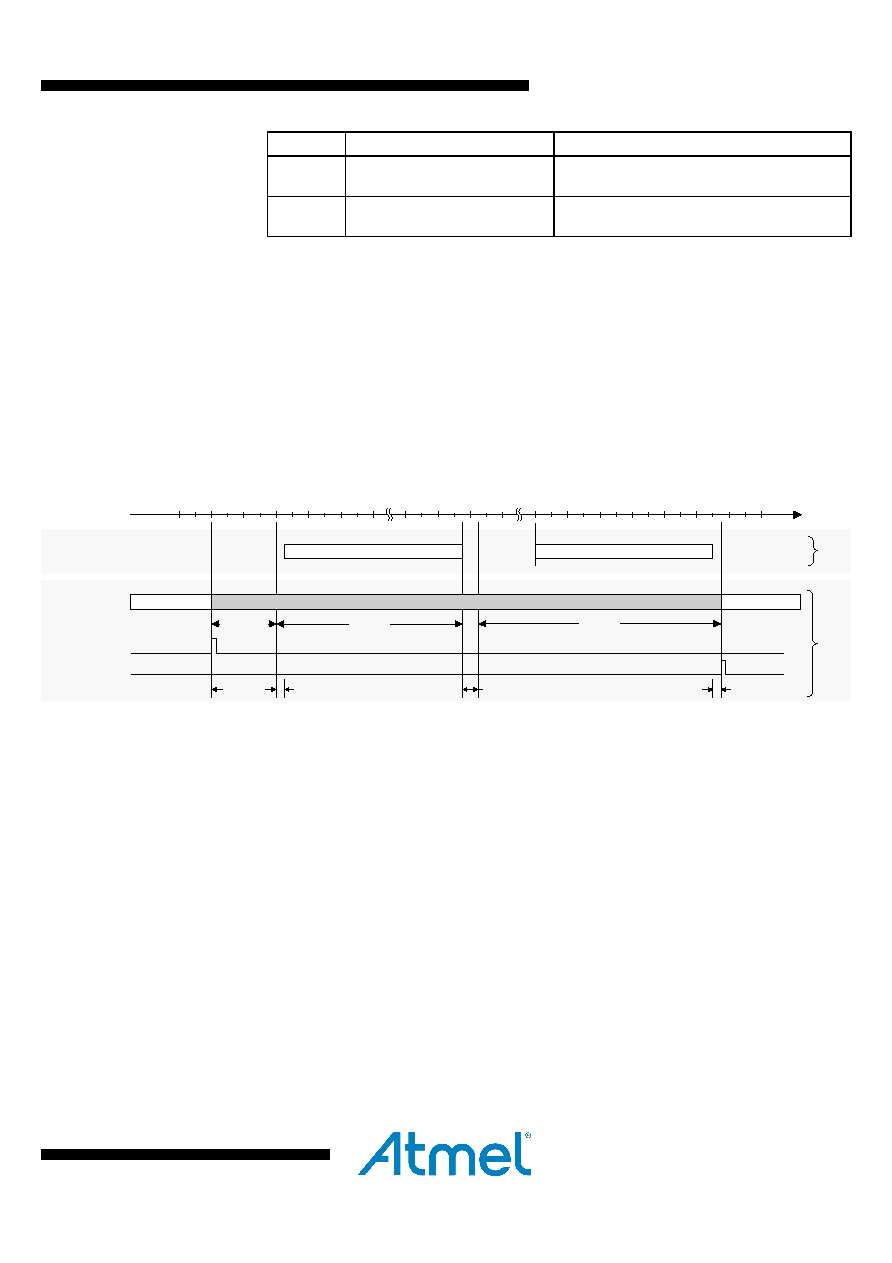

A timing example of a TX_ARET transaction is shown in Figure 9-14 below .

Figure 9-14. Example Timing of a TX_ARET Transaction

R

X

/T

X

F

ra

m

e

o

n

A

ir

TX_ARET_ON

BUSY_TX_ARET

TRX_STATE

FrameType

TX_ARET_ON

RX/TX

RX

RX_END

IRQ

Typ. Processing Delay

16 s

672

0

x

time [s]

128

x+352

SLPTR

TX

tIRQ

Data Frame (Length = 10, ACK=1)

ACK Frame

32 s

tCSMA-CA

TX

CSMA-CA

RX

Note:

1. tCSMA-CA defines the random CSMA-CA processing time.

Here an example data frame of length 10 with an ACK request is transmitted, see Table

9-16 on page 66. After the transmission the radio transceiver switches to receive mode

and expects an acknowledgement response. During the whole transaction including

frame transmit, wait for ACK and ACK receive the radio transceiver status register

TRX_STATUS signals BUSY_TX_ARET.

A

successful

reception

of

the

acknowledgment

frame

is

indicated

by the

TRX24_TX_END interrupt. The status register TRX_STATUS changes back to

TX_ARET_ON. The TX_ARET status register TRAC_STATUS changes as well to

TRAC_STATUS = SUCCESS or TRAC_STATUS = SUCCESS_DATA_PENDING if the

frame pending subfield of the received ACK frame was set to 1.

9.4.2.7 Interrupt Handling

The interrupt handling in the Extended Operating Mode is similar to the Basic Operating

Mode (see section "Interrupt Handling" on page 42). The microcontroller enables

interrupts by setting the appropriate bit in register IRQ_MASK.

For RX_AACK and TX_ARET the following interrupts (Table 9-16 on page 66) inform

about the status of a frame reception and transmission:

相关PDF资料 |

PDF描述 |

|---|---|

| IA3-1206WA00D5 | 0 MHz - 18000 MHz RF/MICROWAVE FIXED ATTENUATOR |

| IA3-0706SS58D0 | 0 MHz - 18000 MHz RF/MICROWAVE FIXED ATTENUATOR |

| IA3-2010SG30D0 | 0 MHz - 18000 MHz RF/MICROWAVE FIXED ATTENUATOR |

| IAC-0706SG04D0 | 0 MHz - 18000 MHz RF/MICROWAVE FIXED ATTENUATOR |

| IAC-0706SS22D0 | 0 MHz - 18000 MHz RF/MICROWAVE FIXED ATTENUATOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| I5108E | 制造商:WINBOND 制造商全称:Winbond 功能描述:SINGLE-CHIP 1 TO 16 MINUTES DURATION VOICE RECORD/PLAYBACK DEVICES WITH DIGITAL STORAGE CAPABILITY |

| I5108EI | 制造商:WINBOND 制造商全称:Winbond 功能描述:SINGLE-CHIP 1 TO 16 MINUTES DURATION VOICE RECORD/PLAYBACK DEVICES WITH DIGITAL STORAGE CAPABILITY |

| I5108S | 制造商:WINBOND 制造商全称:Winbond 功能描述:SINGLE-CHIP 1 TO 16 MINUTES DURATION VOICE RECORD/PLAYBACK DEVICES WITH DIGITAL STORAGE CAPABILITY |

| I5108SI | 制造商:WINBOND 制造商全称:Winbond 功能描述:SINGLE-CHIP 1 TO 16 MINUTES DURATION VOICE RECORD/PLAYBACK DEVICES WITH DIGITAL STORAGE CAPABILITY |

| I5108X | 制造商:WINBOND 制造商全称:Winbond 功能描述:SINGLE-CHIP 1 TO 16 MINUTES DURATION VOICE RECORD/PLAYBACK DEVICES WITH DIGITAL STORAGE CAPABILITY |

发布紧急采购,3分钟左右您将得到回复。