- 您现在的位置:买卖IC网 > PDF目录9903 > IDT72T18105L10BB (IDT, Integrated Device Technology Inc)IC FIFO 131X18 2.5V 10NS 24BGA PDF资料下载

参数资料

| 型号: | IDT72T18105L10BB |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 15/55页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 131X18 2.5V 10NS 24BGA |

| 标准包装: | 1 |

| 系列: | 72T |

| 功能: | 异步,同步 |

| 存储容量: | 2.3K(131 x 18) |

| 数据速率: | 10MHz |

| 访问时间: | 10ns |

| 电源电压: | 2.375 V ~ 2.625 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 240-BGA |

| 供应商设备封装: | 240-PBGA(19x19) |

| 包装: | 托盘 |

| 其它名称: | 72T18105L10BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

22

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72T1845/55/65/75/85/95/105/115/125 2.5V TeraSync 18-BIT/9-BIT FIFO 2Kx18/4Kx9, 4Kx18/

8Kx9, 8Kx18/16Kx9, 16Kx18/32Kx9, 32Kx18/64Kx9, 64Kx18/128Kx9, 128Kx18/256Kx9, 256Kx18/512Kx9, 512Kx18/1Mx9

FEBRUARY 10, 2009

or both together. When

REN and LD are restored to a LOW level, reading of

theoffsetregisterscontinueswhereitleftoff.Itshouldbenoted,andcareshould

be taken from the fact that when a parallel read of the flag offsets is performed,

the data word that was present on the output lines Qn will be overwritten.

Parallel reading of the offset registers is always permitted regardless of

which timing mode (IDT Standard or FWFT modes) has been selected.

RETRANSMIT FROM MARK OPERATION

The Retransmit from Mark feature allows FIFO data to be read repeatedly

startingatauser-selectedposition.TheFIFOisfirstputintoretransmitmodethat

will‘mark’abeginningwordandalsosetapointerthatwillpreventongoingFIFO

write operations from over-writing retransmit data. The retransmit data can be

read repeatedly any number of times from the ‘marked’ position. The FIFO can

be taken out of retransmit mode at any time to allow normal device operation.

The ‘mark’ position can be selected any number of times, each selection over-

writingthepreviousmarklocation.RetransmitoperationisavailableinbothIDT

standard and FWFT modes.

During IDT standard mode the FIFO is put into retransmit mode by a Low-

to-High transition on RCLK when the ‘MARK’ input is HIGH and

EF is HIGH.

The rising RCLK edge ‘marks’ the data present in the FIFO output register as

thefirstretransmitdata.TheFIFOremainsinretransmitmodeuntilarisingedge

on RCLK occurs while MARK is LOW.

Once a ‘marked’ location has been set (and the device is still in retransmit

mode, MARK is HIGH), a retransmit can be initiated by a rising edge on RCLK

while the retransmit input (

RT) is LOW. REN must be HIGH (reads disabled)

before bringing

RTLOW.Thedeviceindicatesthestartofretransmitsetupby

setting

EFLOW,alsopreventingreads.WhenEFgoesHIGH,retransmitsetup

iscompleteandreadoperationsmaybeginstartingwiththefirstdataattheMARK

location. Since IDT standard mode is selected, every word read including the

first ‘marked’ word following a retransmit setup requires a LOW on

REN(read

enabled).

Note, write operations may continue as normal during all retransmit

functions, however write operations to the ‘marked’ location will be prevented.

See Figure 18, Retransmit from Mark (IDT standard mode), for the relevant

timingdiagram.

During FWFT mode the FIFO is put into retransmit mode by a rising RCLK

edge when the ‘MARK’ input is HIGH and

OR is LOW. The rising RCLK edge

‘marks’ the data present in the FIFO output register as the first retransmit data.

The FIFO remains in retransmit mode until a rising RCLK edge occurs while

MARK is LOW.

Once a marked location has been set (and the device is still in retransmit

can be initiated by a rising RCLK edge while the retransmit input (

RT)isLOW.

REN must be HIGH (reads disabled) before bringing RT LOW. The device

indicates the start of retransmit setup by setting

ORHIGH.

When

OR goes LOW, retransmit setup is complete and on the next rising

RCLK edge after retransmit setup is complete, (

RTgoesHIGH),thecontents

of the first retransmit location are loaded onto the output register. Since FWFT

mode is selected, the first word appears on the outputs regardless of

REN, a

LOW on

RENisnotrequiredforthefirstword.Readingallsubsequentwords

requires a LOW on

REN to enable the rising RCLK edge. See Figure 19,

Retransmit from Mark timing (FWFT mode), for the relevant timing diagram.

Note, for the IDT72T1845/72T1855/72T1865/72T1875/72T1885/

72T1895theremustbeaminimumof32bytesofdatabetweenthewritepointer

andreadpointerwhentheMARKisasserted,fortheIDT72T18105/72T18115

there must be a minimum of 128 bytes and for the IDT72T18125 there must be

a minimum of 256 bytes. Remember, 2(x9) bytes = 1(x18) word. (32 bytes =

16 word = 8 long words). Also, once the MARK is set, the write pointer will not

increment past the “marked” location until the MARK is deasserted. This

prevents “overwriting” of retransmit data.

HSTL/LVTTL I/O

Both the write port and read port are user selectable between HSTL or

LVTTL I/O, via two select pins, WHSTL and RHSTL respectively. All other

control pins are selectable via SHSTL, see Table 5 for details of groupings.

Note,thatwhenthewriteportisselectedforHSTLmode,theusercanreduce

the power consumption (in stand-by mode by utilizing the

WCS input).

All “Static Pins” must be tied to VCC or GND. These pins are LVTTL only,

and are purely device configuration pins.

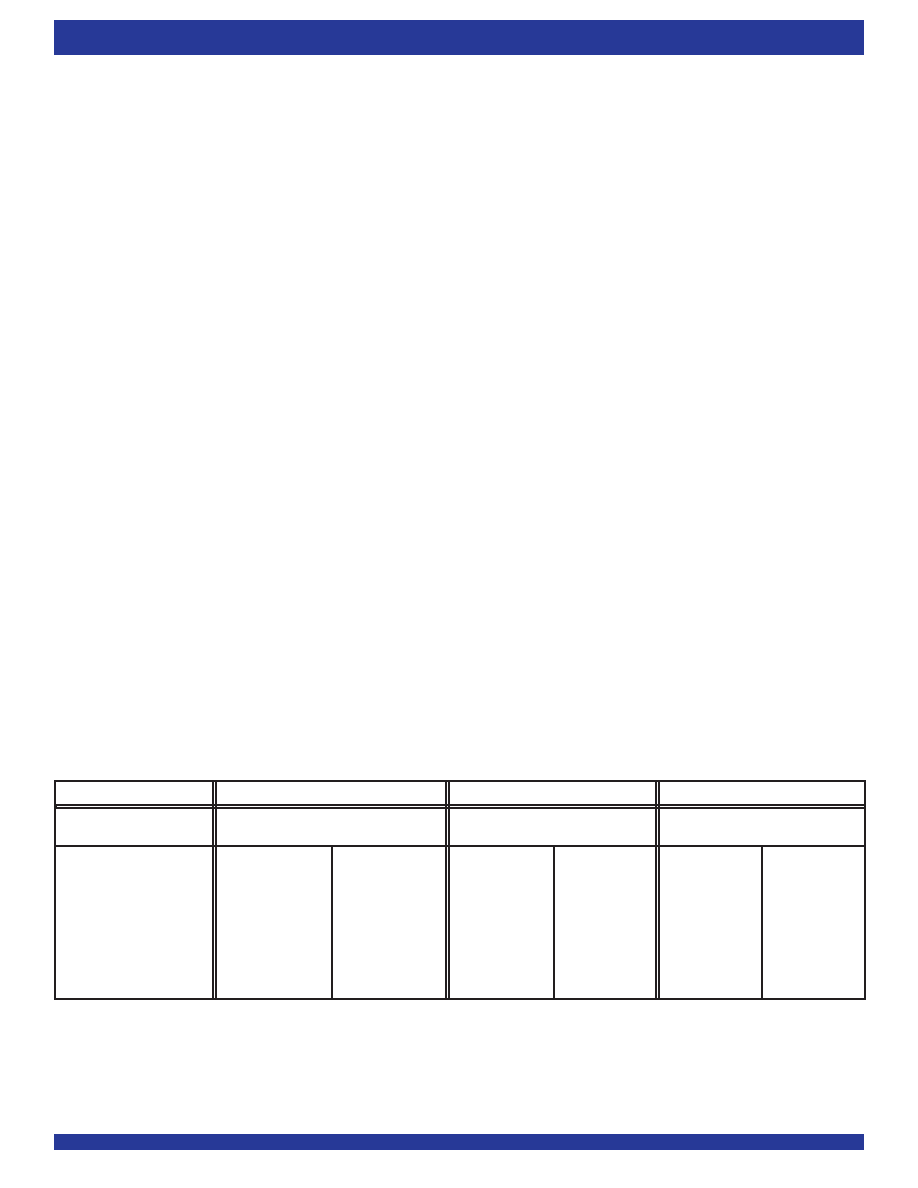

TABLE 5 — I/O CONFIGURATION

WHSTL SELECT

RHSTL SELECT

SHSTL SELECT

STATIC PINS

WHSTL: HIGH = HSTL

RHSTL: HIGH = HSTL

SHSTL: HIGH = HSTL

LVTTL ONLY

LOW = LVTTL

Dn (I/P)

RCLK/RD (I/P)

EF/OR (O/P)

SCLK (I/P)

PRS (I/P)

IW (I/P)

OW (I/P)

WCLK/WR (I/P)

RCS (I/P)

PAF (O/P)

LD (I/P)

TRST (I/P)

BM (I/P)

ASYW (I/P)

WEN (I/P)

MARK (I/P)

EREN (O/P)

MRS (I/P)

TDI (I/P)

ASYR (I/P)

BE (I/P)

WCS (I/P)

REN (I/P)

PAE (O/P)

TCK (I/P)

IP (I/P)

FSEL0 (I/P)

OE (I/P)

FF/IR (O/P)

TMS (I/P)

FSEL1 (I/P)

PFM (I/P)

RT (I/P)

HF (O/P)

SEN (I/P)

SHSTL (I/P)

WHSTL (I/P)

Qn (O/P)

ERCLK (O/P)

FWFT/SI (I/P)

RHSTL (I/P)

TDO (O/P)

相关PDF资料 |

PDF描述 |

|---|---|

| MS27508E14B15PA | CONN RCPT 15POS BOX MNT W/PINS |

| V48A28T500BL2 | CONVERTER MOD DC/DC 28V 500W |

| MS27656T15F35PC | CONN RCPT 37POS WALL MNT W/PINS |

| V48A28T500BL | CONVERTER MOD DC/DC 28V 500W |

| V48A28T500B3 | CONVERTER MOD DC/DC 28V 500W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72T18105L4-4BB | 功能描述:IC FIFO 131X18 2.5V 4NS 240BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T18105L4-4BBG | 功能描述:IC FIFO 131072X18 SYNC 240BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T18105L5BB | 功能描述:IC FIFO 131X18 2.5V 5NS 240BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T18105L5BBGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 131X18 2.5V 5NS 240BGA |

| IDT72T18105L5BBI | 功能描述:IC FIFO 131X18 2.5V 5NS 240BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。