- 您现在的位置:买卖IC网 > PDF目录9903 > IDT72T18105L10BB (IDT, Integrated Device Technology Inc)IC FIFO 131X18 2.5V 10NS 24BGA PDF资料下载

参数资料

| 型号: | IDT72T18105L10BB |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 20/55页 |

| 文件大小: | 0K |

| 描述: | IC FIFO 131X18 2.5V 10NS 24BGA |

| 标准包装: | 1 |

| 系列: | 72T |

| 功能: | 异步,同步 |

| 存储容量: | 2.3K(131 x 18) |

| 数据速率: | 10MHz |

| 访问时间: | 10ns |

| 电源电压: | 2.375 V ~ 2.625 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 240-BGA |

| 供应商设备封装: | 240-PBGA(19x19) |

| 包装: | 托盘 |

| 其它名称: | 72T18105L10BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

27

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72T1845/55/65/75/85/95/105/115/125 2.5V TeraSync 18-BIT/9-BIT FIFO 2Kx18/4Kx9, 4Kx18/

8Kx9, 8Kx18/16Kx9, 16Kx18/32Kx9, 32Kx18/64Kx9, 64Kx18/128Kx9, 128Kx18/256Kx9, 256Kx18/512Kx9, 512Kx18/1Mx9

FEBRUARY 10, 2009

If asynchronous

PAEconfigurationisselected,thePAEisassertedLOW

ontheLOW-to-HIGHtransitionoftheReadClock(RCLK).

PAEisresettoHIGH

ontheLOW-to-HIGHtransitionoftheWriteClock(WCLK).Ifsynchronous

PAE

configuration is selected, the

PAEisupdatedontherisingedgeofRCLK.See

Figure 26, Asynchronous Programmable Almost-Empty Flag Timing (IDT

Standard and FWFT Mode), for the relevant timing information.

HALF-FULL FLAG (

HF)

Thisoutputindicatesahalf-fullFIFO.TherisingWCLKedgethatfillstheFIFO

beyond half-full sets

HF LOW. The flag remains LOW until the difference

between the write and read pointers becomes less than or equal to half of the

totaldepthofthedevice;therisingRCLKedgethataccomplishesthiscondition

sets

HF HIGH.

InIDTStandardmode,ifnoreadsareperformedafterreset(

MRSorPRS),

HF will go LOW after (D/2 + 1) writes to the FIFO. If x18 Input or x18 Output

busWidthisselected,D = 2,048fortheIDT72T1845,4,096fortheIDT72T1855,

8,192 for the IDT72T1865, 16,384 for the IDT72T1875, 32,768 for the

IDT72T1885, 65,536 for the IDT72T1895, 131,072 for the IDT72T18105,

262,144 for the IDT72T18115 and 524,288 for the IDT72T18125. If both x9

Input and x9 Output bus Widths are selected, D = 4,096 for the IDT72T1845,

8,192 for the IDT72T1855, 16,384 for the IDT72T1865, 32,768 for the

IDT72T1875, 65,536 for the IDT72T1885, 131,072 for the IDT72T1895,

262,144 for the IDT72T18105, 524,288 for the IDT72T18115 and 1,048,576

for the IDT72T18125.

In FWFT mode, if no reads are performed after reset (

MRS or PRS), HF

will go LOW after (D-1/2 + 2) writes to the FIFO. If x18 Input or x18 Output bus

Width is selected, D = 2,049 for the IDT72T1845, 4,097 for the IDT72T1855,

8,193 for the IDT72T1865, 16,385 for the IDT72T1875, 32,769 for the

IDT72T1885, 65,537 for the IDT72T1895, 131,073 for the IDT72T18105,

262,145 for the IDT72T18115 and 524,289 for the IDT72T18125. If both x9

Input and x9 Output bus Widths are selected, D = 4,097 for the IDT72T1845,

8,193 for the IDT72T1855, 16,385 for the IDT72T1865, 32,769 for the

IDT72T1875, 65,537 for the IDT72T1885, 131,073 for the IDT72T1895,

262,145 for the IDT72T18105, 524,289 for the IDT72T18115 and 1,048,577

for the IDT72T18125.

See Figure 27, Half-Full Flag Timing (IDT Standard and FWFT Mode),

for the relevant timing information. Because

HFisupdatedbybothRCLKand

WCLK, it is considered asynchronous.

ECHO READ CLOCK (ERCLK)

The Echo Read Clock output is provided in both HSTL and LVTTL mode,

selectable via RHSTL. The ERCLK is a free-running clock output, it will always

follow the RCLK input regardless of

REN, RCS.

The ERCLK output follows the RCLK input with an associated delay. This

delay provides the user with a more effective read clock source when reading

data from the Qn outputs. This is especially helpful at high speeds when

variableswithinthedevicemaycausechangesinthedataaccesstimes.These

variations in access time maybe caused by ambient temperature, supply

voltage, device characteristics. The ERCLK output also compensates for any

tracelengthdelaysbetweentheQndataoutputsandreceivingdevicesinputs.

Anyvariationseffectingthedataaccesstimewillalsohaveacorresponding

effectontheERCLKoutputproducedbytheFIFOdevice,thereforetheERCLK

outputleveltransitionsshouldalwaysbeatthesamepositionintimerelativeto

the data outputs. Note, that ERCLK is guaranteed by design to be slower than

the slowest Qn, data output. Refer to Figure 4, Echo Read Clock and Data

Output Relationship, Figure 28, Echo Read Clock & Read Enable Operation

and Figure 29, Echo RCLK & Echo

REN Operation for timing information.

ECHO READ ENABLE (

EREN)

The Echo Read Enable output is provided in both HSTL and LVTTL mode,

selectable via RHSTL.

The

EREN output is provided to be used in conjunction with the ERCLK

outputandprovidesthereadingdevicewithamoreeffectiveschemeforreading

data from the Qn output port at high speeds. The

ERENoutputiscontrolledby

internal logic that behaves as follows: The

ERENoutputisactiveLOWforthe

RCLK cycle that a new word is read out of the FIFO. That is, a rising edge of

RCLKwillcause

ERENtogoactive,LOWifbothRENandRCSareactive,LOW

and the FIFO is NOT empty.

SERIAL CLOCK (SCLK)

Duringserialloadingoftheprogrammingflagoffsetregisters,arisingedge

on the SCLK input is used to load serial data present on the SI input provided

that the

SENinputisLOW.

DATA OUTPUTS (Q0-Qn)

(Q0 - Q17) data outputs for 18-bit wide data or (Q0 - Q8) data outputs for

9-bit wide data.

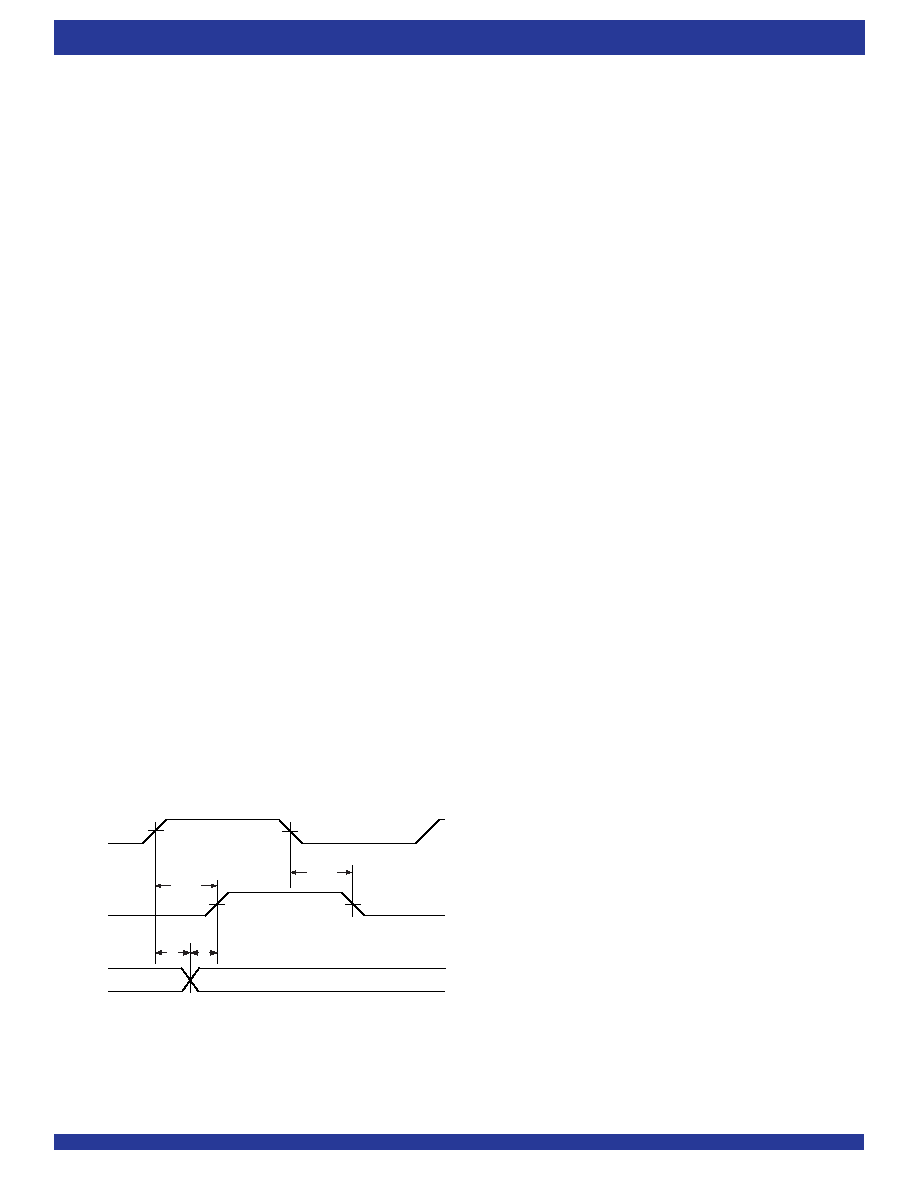

5909 drw08

ERCLK

tA

tD

QSLOWEST(3)

RCLK

tERCLK

Figure 4. Echo Read Clock and Data Output Relationship

NOTES:

1.

REN is LOW;RCS is LOW.

2. tERCLK > tA, guaranteed by design.

3. Qslowest is the data output with the slowest access time, tA.

4. Time, tD is greater than zero, guaranteed by design.

相关PDF资料 |

PDF描述 |

|---|---|

| MS27508E14B15PA | CONN RCPT 15POS BOX MNT W/PINS |

| V48A28T500BL2 | CONVERTER MOD DC/DC 28V 500W |

| MS27656T15F35PC | CONN RCPT 37POS WALL MNT W/PINS |

| V48A28T500BL | CONVERTER MOD DC/DC 28V 500W |

| V48A28T500B3 | CONVERTER MOD DC/DC 28V 500W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72T18105L4-4BB | 功能描述:IC FIFO 131X18 2.5V 4NS 240BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T18105L4-4BBG | 功能描述:IC FIFO 131072X18 SYNC 240BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T18105L5BB | 功能描述:IC FIFO 131X18 2.5V 5NS 240BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72T18105L5BBGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 131X18 2.5V 5NS 240BGA |

| IDT72T18105L5BBI | 功能描述:IC FIFO 131X18 2.5V 5NS 240BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72T 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。