- 您现在的位置:买卖IC网 > PDF目录10950 > IDT821054PQFG (IDT, Integrated Device Technology Inc)IC PCM CODEC QUAD MPI 64-PQFP PDF资料下载

参数资料

| 型号: | IDT821054PQFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 3/45页 |

| 文件大小: | 0K |

| 描述: | IC PCM CODEC QUAD MPI 64-PQFP |

| 标准包装: | 84 |

| 类型: | PCM 编解码器/滤波器 |

| 数据接口: | PCM 音频接口 |

| ADC / DAC 数量: | 4 / 4 |

| 三角积分调变: | 无 |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 4.75 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-QFP |

| 供应商设备封装: | 64-PQFP(14x14) |

| 包装: | 管件 |

| 其它名称: | 800-2516-5 821054PQFG IDT821054PQFG-ND |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

11

IDT821054 QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE

INDUSTRIAL TEMPERATURE RANGE

2.2

DSP PROGRAMMING

2.2.1

SIGNAL PROCESSING

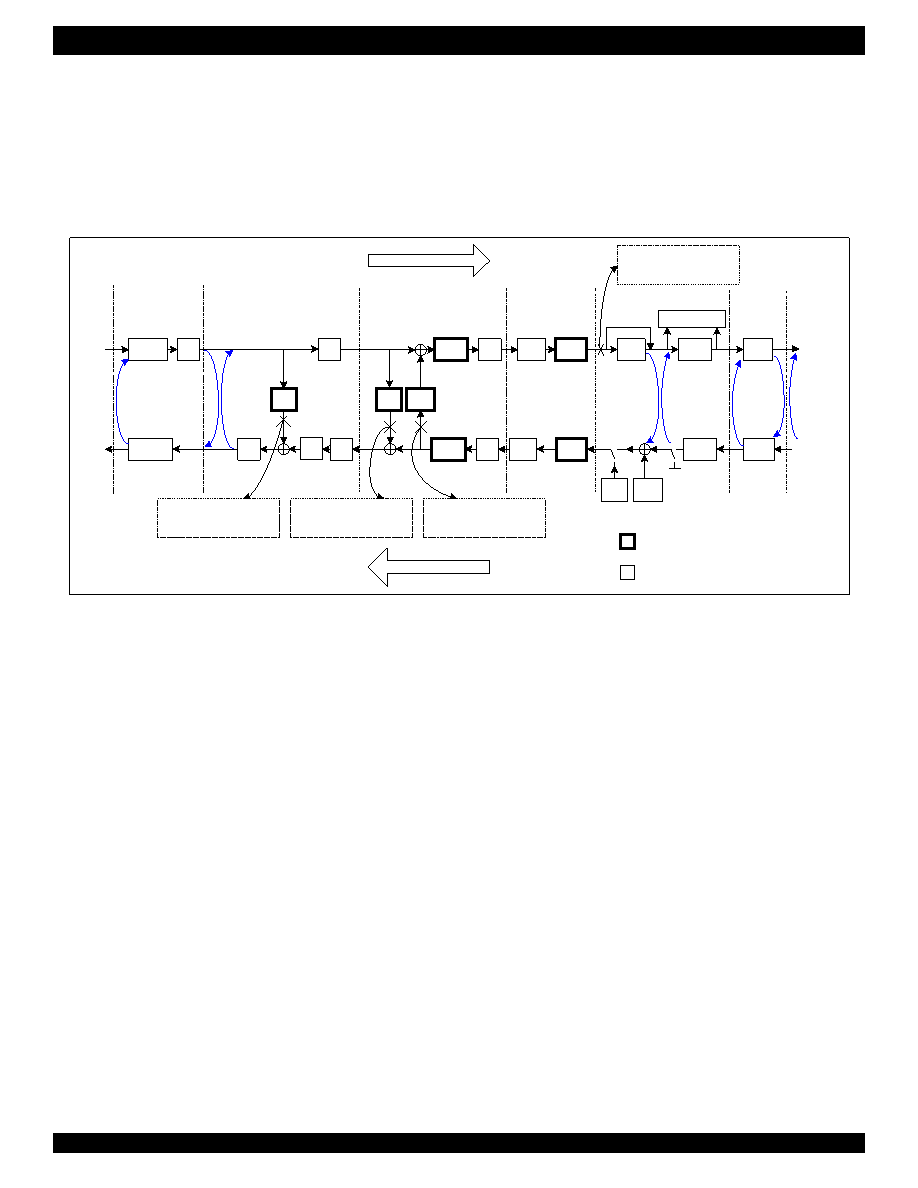

Several blocks are programmable for signal processing. This allows

users to optimize the performance of the IDT821054 for the system.

Figure - 4 shows the signal flow for each channel and indicates the

programmable blocks.

The programmable digital filters are used to adjust gain and

impedance, balance transhybrid and correct frequency response. All the

coefficients of the digital filters can be calculated automatically by a

software provided by IDT. When users provide accurate SLIC model,

impedance and gain requirements, this software will calculate all the

coefficients automatically. After loading these coefficients to the

coefficient RAM of the IDT821054, the final AC characteristics of the line

card (consists of SLIC and CODEC) will meet the ITU-T specifications.

Figure - 4 Signal Flow for Each Channel

Abbreviation List:

LPF/AA: Anti-Alias Low-pass Filter

LPF/SC: Smoothing Low-pass Filter

LPF: Low-pass Filter

HPF: High-pass Filter

GIS: Gain for Impedance Scaling

D1: 1st Down Sample Stage

D2: 2nd Down Sample Stage

U1: 1st Up Sample Stage

U2: 2nd Up Sample Stage

UF: Up Sampling Filter (64 k - 128 k)

IMF: Impedance Matching Filter

ECF: Echo Cancellation Filter

GTX: Gain for Transmit Path

GRX: Gain for Receive Path

FRX: Frequency Response Correction for Transmit

FRR: Frequency Response Correction for Receive

CMP: Compression

EXP: Expansion

TSA: Time Slot Assignment

2.2.2

GAIN ADJUSTMENT

The analog gain and digital gain of each channel can be adjusted

separately in the IDT821054.

For each individual channel, the analog A/D gain in the transmit path

can be selected as 0 dB or 6 dB. The selection is done by the GAD bit in

LREG9. It is 0 dB by default.

For each individual channel, the analog D/A gain in the receive path

can be selected as 0 dB or -6 dB. The selection is done by the GDA bit

in LREG9. It is 0 dB by default.

For each individual channel, the digital gain in the transmit path

(GTX) is programmable from -3 dB to +12 dB with minimum 0.1 dB step.

If the CS[5] bit in local register LREG1 is ‘0’, the GTX filter is disabled. If

the CS[5] bit is ‘1’, the GTX is programmed by the coefficient RAM.

For each individual channel, the digital gain in the receive path

(GRX) is programmable from -12 dB to +3 dB with minimum 0.1 dB step.

If the CS[7] bit in LREG1 is ‘0’, the GRX filter is disabled. If the CS[7] bit

is ‘1’, the GRX is programmed by the coefficient RAM.

2.2.3

IMPEDANCE MATCHING

The IDT821054 provides a programmable feedback path from VIN to

VOUT for each channel. This feedback synthesizes the two-wire

impedance of the SLIC. The programmable Impedance Matching Filter

(IMF) and Gain of Impedance Scaling filter (GIS) work together to realize

impedance matching. If the CS[0] bit in LREG1 is ‘0’, the IMF is

disabled. If the CS[0] bit is ‘1’, the IMF coefficient is programmed by the

coefficient RAM. If the CS[2] bit in LREG1 is ‘0’, the GIS filter is disabled.

If the CS[2] bit is ‘1’, the GIS coefficient is programmed by the coefficient

RAM.

LPF/AA

GTX

D2

LPF

FRX

HPF

CMP

TSA

LPF/SC

∑

U1

GRX

U2

LPF

FRR

Dual

Tone

EXP

TSA

UF

∑

GIS

Level Meter

IMF

ECF

D

LB-

ANA

ALB-

8K

DLB-

8K

DLB

-PC

M

ALB-

DI

DL

B-DI

Receive Path

Transmit Path

VIN

VOUT

Analog

@2 MHz

D1

@64 KHz

@16 KHz

@8 KHz

TS

PCM Highway

DX1/DX2

DR1/DR2

LREG1: CS[2]

CS[2] = 1: enable (normal)

CS[2] = 0: disable (cut)

LREG1: CS[0]

CS[0] = 1: enable (normal)

CS[0] = 0: disable (cut)

LREG1: CS[1]

CS[1] = 1: enable (normal)

CS[1] = 0: disable (cut)

Bold Black Framed: Programmable Filters

Fine Black Framed: Fixed Filters

LREG1: CS[3]

CS[3] = 1: enable (normal)

CS[3] = 0: disable (bypass)

CUT-OFF-PCM

ALB-

1BIT

DLB_1BI

T

FSK

相关PDF资料 |

PDF描述 |

|---|---|

| MCIMX357CVM5BR2 | IC MPU I.MX35 400MAPBGA |

| MCIMX357CVM5B | IC MPU I.MX35 400MAPBGA |

| MCIMX357CJQ5CR2 | MULTIMEDIA PROCESSOR 400-MAPBGA |

| MCF5270CVM150J | IC MCU 32BIT 150MHZ 196-MAPBGA |

| ADV202BBCZ-150 | IC VIDEO CODEC JPEG2000 144CSBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT821064 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE |

| IDT821064PQF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE |

| IDT821068 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC |

| IDT821068PX | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC |

| IDT821621 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:LONG HAUL SLIC |

发布紧急采购,3分钟左右您将得到回复。