- 您现在的位置:买卖IC网 > PDF目录10950 > IDT821054PQFG (IDT, Integrated Device Technology Inc)IC PCM CODEC QUAD MPI 64-PQFP PDF资料下载

参数资料

| 型号: | IDT821054PQFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 7/45页 |

| 文件大小: | 0K |

| 描述: | IC PCM CODEC QUAD MPI 64-PQFP |

| 标准包装: | 84 |

| 类型: | PCM 编解码器/滤波器 |

| 数据接口: | PCM 音频接口 |

| ADC / DAC 数量: | 4 / 4 |

| 三角积分调变: | 无 |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 4.75 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-QFP |

| 供应商设备封装: | 64-PQFP(14x14) |

| 包装: | 管件 |

| 其它名称: | 800-2516-5 821054PQFG IDT821054PQFG-ND |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

15

IDT821054 QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE

INDUSTRIAL TEMPERATURE RANGE

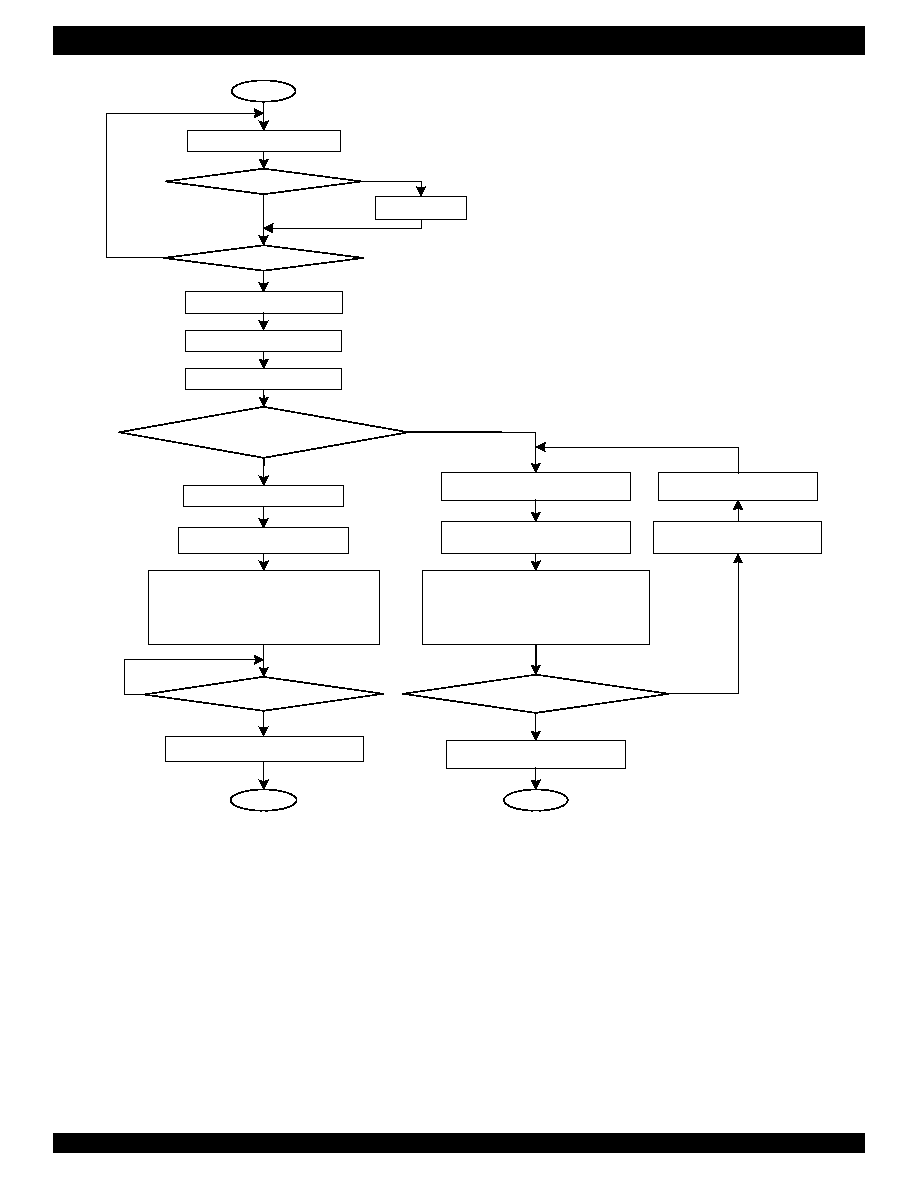

Figure - 7 A Recommended Procedure of Programming the FSK Generator

2.10

LEVEL METERING

The IDT821054 integrates a level meter which is shared by all 4

channels. The level meter is designed to emulate the off-chip PCM test

equipment so as to facilitate the line-card, subscriber line and users

telephone set monitoring. The level meter tests the return signal and

reports the measurement result via the MPI interface. When combined

with tone generation and loopbacks, it allows the microprocessor to test

the channel integrity. The signal on the channel selected by the CS[1:0]

bits in GREG21 will be metered.

The level meter is enabled by setting the LMO bit in GREG21 to ‘1’. A

level meter counter register (GREG20) is used to set the value of time

cycles for sampling the PCM data (8 kHz sampling rate). The output of

level meter is sent to the level meter result registers GREG18 and

GREG19. The LVLL[7:0] bits in GREG18 contain the lower 7 bits of the

result and a data-ready bit (LVLL[0]), while the LVLH[7:0] bits in

GREG19 contain the higher 8 bits of the result. An internal accumulator

sums the rectified samples until the value set in GREG20 is reached. By

then, the LVLL[0] bit is set to ‘1’ and accumulation result is latched into

GREG18 and GREG19 simultaneously.

Once the higher byte of result (GREG19) is read, the LVLL[0] bit in

GREG18 will be reset. It will be set to ‘1’ again by a new data available.

The contents of GREG18 and GREG19 will be overwritten by the

following metering result if they have not been read out yet. To read the

level meter result registers, it is recommended to read GREG18 (lower

byte of result) first.

The L/C bit in GREG21 determines the level meter operation mode. If

the L/C bit is ‘1’, it means that metering mode is selected. In this mode,

Read FO and FS bit in GREG17

FO = 1 ?

FS = 0 ?

Set FO = 1

Set "Seizure Length" in GREG15

Set "Mark Length" in GREG16

Set "Flag Length" in GREG13

Total message data

≤ 64 bytes ?

Set "Data Length" in GREG14

Write message data into FSK-RAM

In GREG17:

Set FCS[2:0] bits to select FSK channel

Set BS bit to select specification (Bellcore or BT)

Set MAS = 0

Set FS = 1

GREG14: Set "Data Length" at this time

Write message data to be sent at this

time to FSK-RAM

In GREG17:

Set FCS[2:0] bits to select FSK channel

Set BS bit to select specification (Bellcore or BT)

Set MAS = 1

Set FS = 1

Finish sending all the message data ?

GREG17: MAS = 0; FO = 0

End

GREG15: Set "Seizure Length" to 0

GREG16: Set "Mark Length" to 0

End

Start

N

Y

Finish sending message data ?

GREG17: FO = 0

Y

N

Y

N

Y

N

Y

N

相关PDF资料 |

PDF描述 |

|---|---|

| MCIMX357CVM5BR2 | IC MPU I.MX35 400MAPBGA |

| MCIMX357CVM5B | IC MPU I.MX35 400MAPBGA |

| MCIMX357CJQ5CR2 | MULTIMEDIA PROCESSOR 400-MAPBGA |

| MCF5270CVM150J | IC MCU 32BIT 150MHZ 196-MAPBGA |

| ADV202BBCZ-150 | IC VIDEO CODEC JPEG2000 144CSBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT821064 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE |

| IDT821064PQF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE |

| IDT821068 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC |

| IDT821068PX | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC |

| IDT821621 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:LONG HAUL SLIC |

发布紧急采购,3分钟左右您将得到回复。