- 您现在的位置:买卖IC网 > PDF目录10950 > IDT821054PQFG (IDT, Integrated Device Technology Inc)IC PCM CODEC QUAD MPI 64-PQFP PDF资料下载

参数资料

| 型号: | IDT821054PQFG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/45页 |

| 文件大小: | 0K |

| 描述: | IC PCM CODEC QUAD MPI 64-PQFP |

| 标准包装: | 84 |

| 类型: | PCM 编解码器/滤波器 |

| 数据接口: | PCM 音频接口 |

| ADC / DAC 数量: | 4 / 4 |

| 三角积分调变: | 无 |

| 电压 - 电源,模拟: | 4.75 V ~ 5.25 V |

| 电压 - 电源,数字: | 4.75 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-QFP |

| 供应商设备封装: | 64-PQFP(14x14) |

| 包装: | 管件 |

| 其它名称: | 800-2516-5 821054PQFG IDT821054PQFG-ND |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

13

IDT821054 QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE

INDUSTRIAL TEMPERATURE RANGE

channels’ SI1 and SI2 status changes can be cleared by applying a read

operation to GREG9. If SB1, SB2 and SB3 pins are configured as

inputs, a read operation to GREG10, GREG11 and GREG12 clears the

interrupt generated by the corresponding SB port of all four channels. A

read operation to LREG4 clears all 7 interrupt sources of the specified

channel.

2.6

DEBOUNCE FILTERS

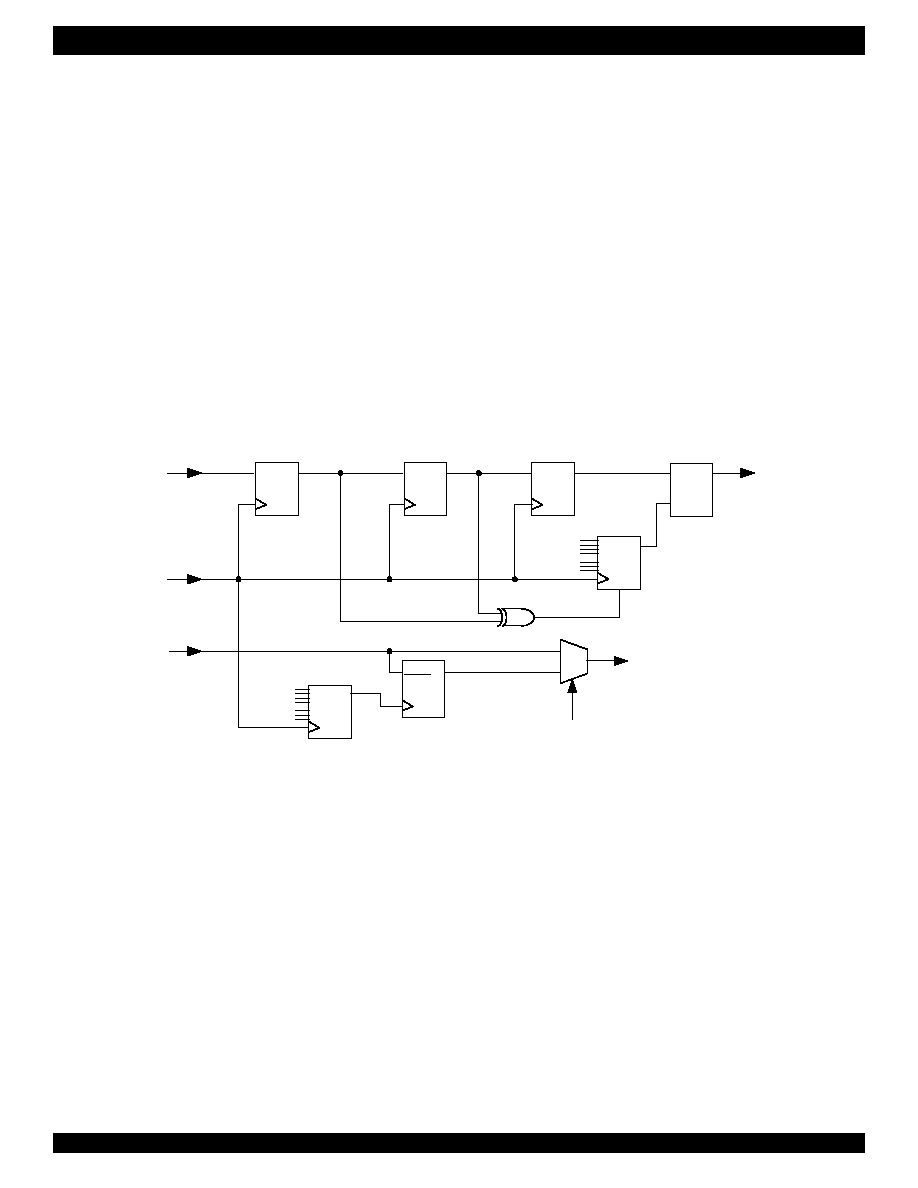

For each channel, the IDT821054 provides two debounce filter

circuits: Debounced Switch Hook (DSH) Filter for the SI1 signal and

Ground Key (GK) Filter for the SI2 signal. See Figure - 5 for details. The

two debounce filters are used to buffer the input signals on SI1 and SI2

pins before changing the state of the SLIC Debounced Input SI1/SI2

Register (GREG9). The Frame Sync (FS) signal is necessary for both

DSH and GK filters.

The DSH[3:0] bits in LREG3 are used to program the debounce

period of the SI1 input of the corresponding channel. The DSH filter is

initially clocked at half of the frame sync rate (250 s). Any data

changing at this sample rate resets a counter that clocks at the rate of 2

ms. The value of the counter is programmable from 0 to 30 via LREG3.

The debounced SI1 signals of Channel 4 to 1 are written to the SIA[3:0]

bits in GREG9. The corresponding SIA bit will not be updated until the

value of the counter is reached. The SI1 pin usually contains the SLIC

switch hook status.

The GK[3:0] bits in LREG3 are used to program the debounce

interval of the SI2 input of the corresponding channel. The debounced

SI2 signals of Channel 4 to 1 are written to the SIB[3:0] bits in GREG9.

The GK debounce filter consists of a six-state up/down counter that

ranges between 0 and 6. This counter is clocked by the GK timer at the

sampling period of 0-30 ms, which is programmed via LREG3. If the

sampled value is low, the value of the counter will be decremented by

each clock pulse. If the sampled value is high, the value of the counter is

incremented by each clock pulse. When the value increases to 6, it sets

a latch whose output is routed to the corresponding SIB bit. If the value

decreases to 0, the latch will be cleared and the output bit will be set to

0. In other cases, the latch and the SIB status remain in their previous

state without being changed. In this way, at least six consecutive GK

clocks with the debounce input remaining at the same state can effect

an output change.

Figure - 5 Debounce Filter

2.7

CHOPPER CLOCK

The IDT821054 provides two programmable chopper clock outputs

CHCLK1 and CHCLK2. They can be used to drive the power supply

switching regulators on SLICs. The two chopper clocks are synchronous

to MCLK. The CHCLK1 outputs a signal which clock cycle is

programmable from 2 to 28 ms. The CHCLK2 outputs a signal which

frequency can be 256 kHz, 512 kHz or 16.384 MHz. The frequencies of

the two chopper clocks are programmed by global register GREG5.

2.8

DUAL TONE AND RING GENERATION

The IDT821054 provides two tone generators (tone generator 0 and

tone generator 1) for each channel. They can produce signals such as

test tone, DTMF, dial tone, busy tone, congestion tone and Caller-ID

Alerting Tone, and output it to the VOUT pin.

The dual tone generators of each channel can be enabled by setting

the TEN0 and TEN1 bits in LREG10 to ‘1’respectively.

The frequency and amplitude of the tone signal are programmed by

the Coe-RAM. The frequency and amplitude coefficients are calculated

by the following formulas:

Frequency coefficient = 32767

cos(f / 8000 2 π)

Amplitude coefficient = A

32767 sin(f / 8000 2 π)

Herein, 'f' is the desired frequency of the tone signal, 'A' is the scaling

parameter of the amplitude. The range of 'A' is from 0 to 1.

A = 1, corresponds to the maximum amplitude of 1.57 V.

A = 0, corresponds to the minimum amplitude of 0 V.

It is a linear relationship between 'A' and the amplitude. That is, if

A=

β ( 0<β<1), the amplitude will be 1.57 β (V).

The frequency range is from 25 Hz to 3400 Hz. The frequency

tolerances are as the following:

25 Hz < f < 40 Hz, tolerance <

±12%

DQ

E

DQ

DSH[3:0]

Debounce

Period

(0-30 ms)

DQ

GK[3:0]

Debounce

Interval

(0-30 ms)

up/

down

Q

6 states

Up/down

Counter

7 bit Debounce

Counter

7 bit Debounce

Counter

= 0

≠ 0

GK

SIB

SIA

SI1

4 kHz

SI2

RST

FS/2

相关PDF资料 |

PDF描述 |

|---|---|

| MCIMX357CVM5BR2 | IC MPU I.MX35 400MAPBGA |

| MCIMX357CVM5B | IC MPU I.MX35 400MAPBGA |

| MCIMX357CJQ5CR2 | MULTIMEDIA PROCESSOR 400-MAPBGA |

| MCF5270CVM150J | IC MCU 32BIT 150MHZ 196-MAPBGA |

| ADV202BBCZ-150 | IC VIDEO CODEC JPEG2000 144CSBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT821064 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE |

| IDT821064PQF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH GCI INTERFACE |

| IDT821068 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC |

| IDT821068PX | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL PROGRAMMABLE PCM CODEC |

| IDT821621 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:LONG HAUL SLIC |

发布紧急采购,3分钟左右您将得到回复。