- 您现在的位置:买卖IC网 > PDF目录296249 > IS42VS16160D-75BLI (INTEGRATED SILICON SOLUTION INC) 16M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 PDF资料下载

参数资料

| 型号: | IS42VS16160D-75BLI |

| 厂商: | INTEGRATED SILICON SOLUTION INC |

| 元件分类: | DRAM |

| 英文描述: | 16M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 |

| 封装: | 13 X 8 MM, 0.80 MM PITCH, LEAD FREE, MS-207, BGA-54 |

| 文件页数: | 12/61页 |

| 文件大小: | 939K |

| 代理商: | IS42VS16160D-75BLI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页

2

Integrated Silicon Solution, Inc. — www.issi.com

Rev. 00A

04/21/09

IS42VS83200D, IS42VS16160D

IS45VS83200D, IS45VS16160D

DEVICE OVERVIEW

The 256Mb SDRAM is a high speed CMOS, dynamic

random-accessmemorydesignedtooperatein1.8VVdd

and1.8VVddq memorysystemscontaining268,435,456

bits.Internallyconfiguredasaquad-bankDRAMwitha

synchronousinterface.Each67,108,864-bitbankisorga-

nizedas8,192rowsby512columnsby16bitsor8,192

rowsby1,024columnsby8bits.

The256MbSDRAMincludesanAUTOREFRESHMODE,

and a power-saving, power-down mode. All signals are

registeredonthepositiveedgeoftheclocksignal,CLK.

AllinputsandoutputsareLVCMOScompatible.

The256MbSDRAMhastheabilitytosynchronouslyburst

data at a high data rate with automatic column-address

generation, the ability to interleave between internal banks

to hide precharge time and the capability to randomly

change column addresses on each clock cycle during

burst access.

A self-timed row precharge initiated at the end of the burst

sequenceisavailablewiththeAUTOPRECHARGEfunction

enabled. Precharge one bank while accessing one of the

other three banks will hide the precharge cycles and provide

seamless, high-speed, random-access operation.

SDRAM read and write accesses are burst oriented starting

at a selected location and continuing for a programmed

number of locations in a programmed sequence. The

registration of an ACTIVE command begins accesses,

followedbyaREADorWRITEcommand.TheACTIVE

command in conjunction with address bits registered are

usedtoselectthebankandrowtobeaccessed(BA0,

BA1selectthebank;A0-A12selecttherow).TheREAD

or WRITE commands in conjunction with address bits

registered are used to select the starting column location

for the burst access.

ProgrammableREADorWRITEburstlengthsconsistof

1,2,4and8locationsorfullpage,withaburstterminate

option.

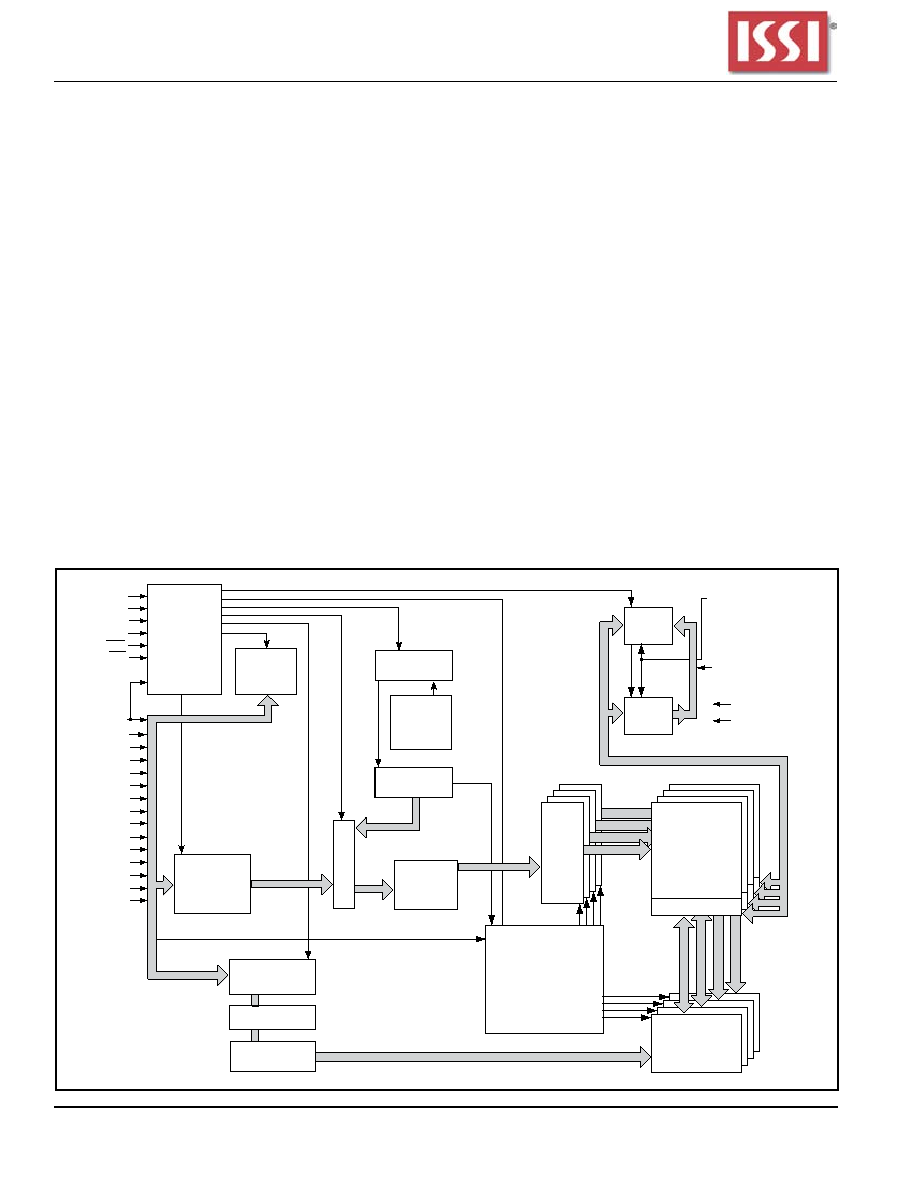

CLK

CKE

CS

RAS

CAS

WE

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

BA0

BA1

A10

A12

COMMAND

DECODER

&

CLOCK

GENERATOR

MODE

REGISTER

REFRESH

CONTROLLER

REFRESH

COUNTER

SELF

REFRESH

CONTROLLER

ROW

ADDRESS

LATCH

MUL

TIPLEXER

COLUMN

ADDRESSLATCH

BURSTCOUNTER

COLUMN

ADDRESSBUFFER

COLUMNDECODER

DATAIN

BUFFER

DATAOUT

BUFFER

DQML

DQMH

DQ0-15

VDD/VDDQ

Vss/VssQ

13

9

13

9

16

512

(x16)

8192

R

O

WDECODER

8192

MEMORYCELL

ARRAY

BANK 0

SENSEAMPI/OGATE

BANKCONTROLLOGIC

ROW

ADDRESS

BUFFER

A11

2

FUNCTIONAL BLOCK DIAGRAM (FOR 4Mx16x4 BANKS SHOWN)

相关PDF资料 |

PDF描述 |

|---|---|

| IS45VS16160D-8BLA2 | 16M X 16 SYNCHRONOUS DRAM, 6 ns, PBGA54 |

| IS43R32800B-5BL | 8M X 32 DDR DRAM, 0.7 ns, PBGA144 |

| IS61C512-25TI | x8 SRAM |

| IS61C512-35J | x8 SRAM |

| IS61C512-35JI | x8 SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IS42VS16400C1 | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42VS16400C1-10T | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42VS16400C1-10TL | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42VS16400C1-10TLI | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

| IS42VS16400C1-12T | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM |

发布紧急采购,3分钟左右您将得到回复。