- 您现在的位置:买卖IC网 > PDF目录45323 > MP80C31-12D (ATMEL CORP) 8-BIT, 12 MHz, MICROCONTROLLER, PDIP40 PDF资料下载

参数资料

| 型号: | MP80C31-12D |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 12 MHz, MICROCONTROLLER, PDIP40 |

| 封装: | PLASTIC, DIP-40 |

| 文件页数: | 126/170页 |

| 文件大小: | 4133K |

| 代理商: | MP80C31-12D |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页当前第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页

59

ATtiny4/5/9/10 [DATASHEET]

8127F–AVR–02/2013

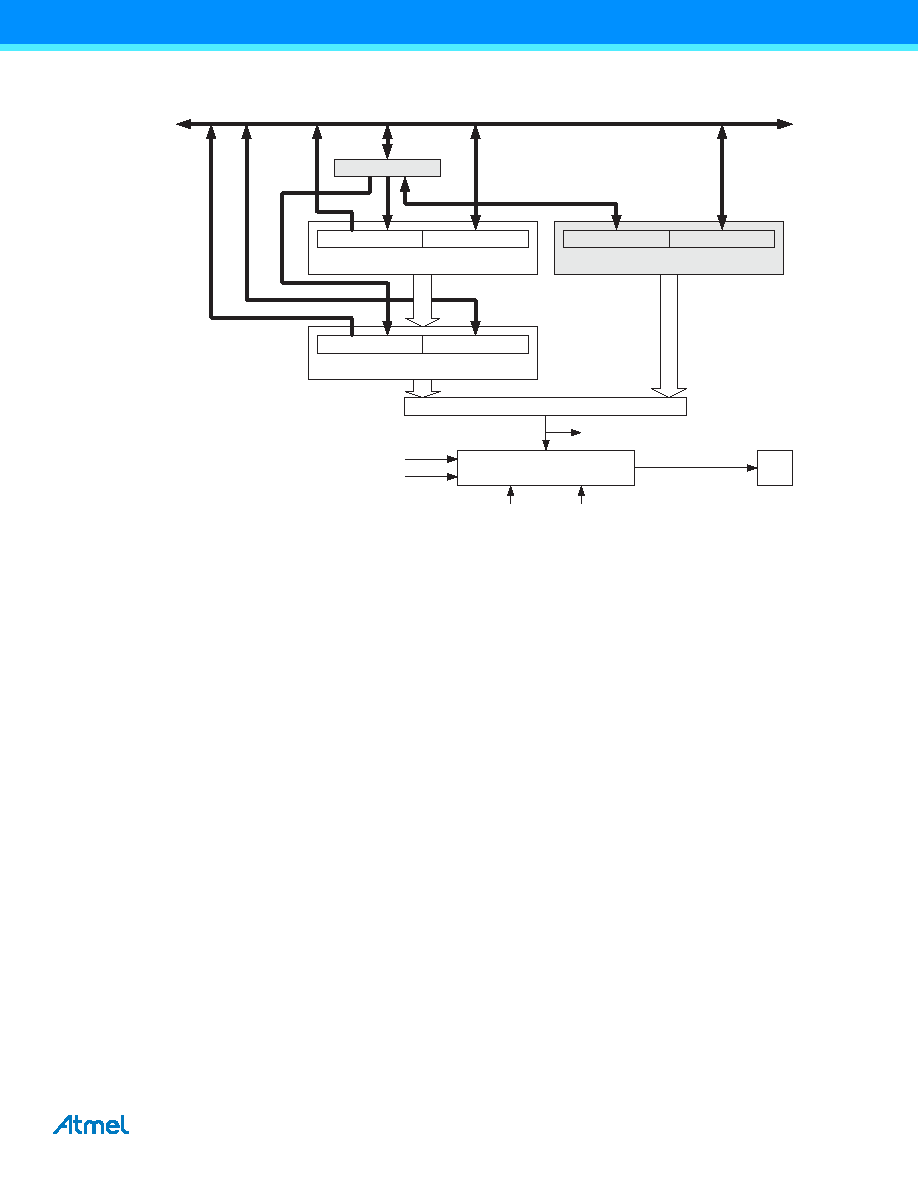

Figure 11-6.

Output Compare Unit, Block Diagram

The OCR0x Register is double buffered when using any of the twelve Pulse Width Modulation (PWM) modes. For

the Normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double

buffering synchronizes the update of the OCR0x Compare Register to either TOP or BOTTOM of the counting

sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby

making the output glitch-free.

The OCR0x Register access may seem complex, but this is not case. When the double buffering is enabled, the

CPU has access to the OCR0x Buffer Register, and if double buffering is disabled the CPU will access the OCR0x

directly. The content of the OCR0x (Buffer or Compare) Register is only changed by a write operation (the

Timer/Counter does not update this register automatically as the TCNT0 and ICR0 Register). Therefore OCR0x is

not read via the high byte temporary register (TEMP). However, it is a good practice to read the low byte first as

when accessing other 16-bit registers. Writing the OCR0x Registers must be done via the TEMP Register since the

compare of all 16 bits is done continuously. The high byte (OCR0xH) has to be written first. When the high byte I/O

location is written by the CPU, the TEMP Register will be updated by the value written. Then when the low byte

(OCR0xL) is written to the lower eight bits, the high byte will be copied into the upper 8-bits of either the OCR0x

buffer or OCR0x Compare Register in the same system clock cycle.

For more information of how to access the 16-bit registers refer to “Accessing 16-bit Registers” on page 70.

11.6.1

Force Output Compare

In non-PWM Waveform Generation modes, the match output of the comparator can be forced by writing a one to

the Force Output Compare (0x) bit. Forcing compare match will not set the OCF0x flag or reload/clear the timer,

but the OC0x pin will be updated as if a real compare match had occurred (the COM01:0 bits settings define

whether the OC0x pin is set, cleared or toggled).

OCFnx (Int.Req.)

= (16-bit Comparator )

OCRnx Buffer (16-bit Register)

OCRnxH Buf. (8-bit)

OCnx

TEMP (8-bit)

DATA BUS (8-bit)

OCRnxL Buf. (8-bit)

TCNTn (16-bit Counter)

TCNTnH (8-bit)

TCNTnL (8-bit)

COMnx1:0

WGMn3:0

OCRnx (16-bit Register)

OCRnxH (8-bit)

OCRnxL (8-bit)

Waveform Generator

TOP

BOTTOM

相关PDF资料 |

PDF描述 |

|---|---|

| MF280C51-20R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 |

| MS80C51-30R | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQCC44 |

| MS80C51-20D | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQCC44 |

| MF280C31-25R | 8-BIT, 25 MHz, MICROCONTROLLER, PQFP44 |

| MF180C31-16D | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MP81 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:BRIDGE RECTIFIERS |

| MP810 | 制造商:GOOD-ARK 制造商全称:GOOD-ARK Electronics 功能描述:SILICON BRIDGE RECTIFIERS |

| MP-810 | 制造商:JAMECO BENCHPRO 功能描述:4-Piece Plier/Cutter/Screwdrivers Set |

| MP8100 | 制造商:MPS 制造商全称:Monolithic Power Systems 功能描述:Precision High-Side Current-Sense Amplifier |

| MP8100DS | 制造商:MPS 制造商全称:Monolithic Power Systems 功能描述:Precision High-Side Current-Sense Amplifier |

发布紧急采购,3分钟左右您将得到回复。