- 您现在的位置:买卖IC网 > PDF目录385639 > MT48LC2M32LFFC (Micron Technology, Inc.) 512K x 32 x 4 banks 3.3v SDRAM(3.3V,512K x 32 x 4组同步动态RAM) PDF资料下载

参数资料

| 型号: | MT48LC2M32LFFC |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | 512K x 32 x 4 banks 3.3v SDRAM(3.3V,512K x 32 x 4组同步动态RAM) |

| 中文描述: | 为512k × 32 × 4银行3.3V的内存电压(3.3V,512K采样× 32 × 4组同步动态RAM)的 |

| 文件页数: | 16/50页 |

| 文件大小: | 1054K |

| 代理商: | MT48LC2M32LFFC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页

16

64Mb: x32, 3.3V SDRAM

BatRam_3V.p65 – Rev. 0.7, Pub. 2/01

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2001, Micron Technology, Inc.

64Mb: x32, 3.3V

SDRAM

PRELIMINARY

READ

NOP

NOP

WRITE

NOP

CLK

T2

T1

T4

T3

T0

DQM

DQ

D

OUT

n

COMMAND

D

IN

b

ADDRESS

BANK,

COL

n

BANK,

COL

b

DS

t

t

HZ

t

CK

NOTE:

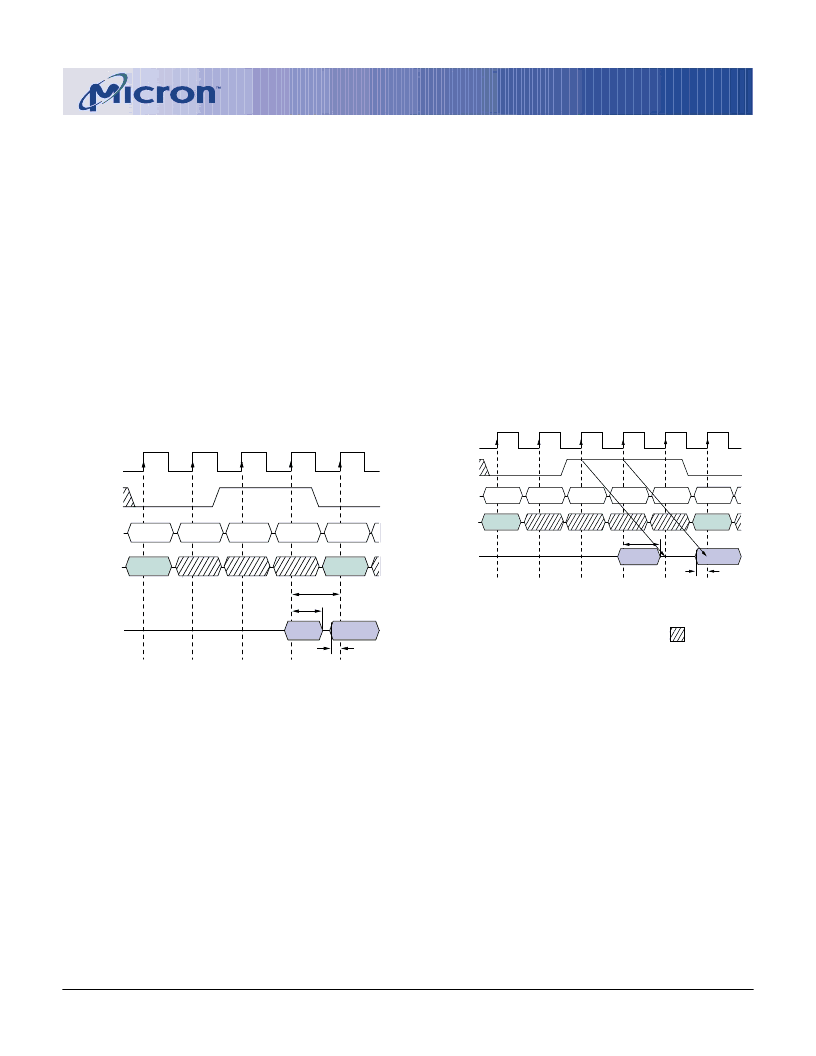

A CAS latency of three is used for illustration. The

READ

command may be to any bank, and the WRITE command

may be to any bank. If a burst of one is used, then DQM is

not required.

DON’T CARE

READ

NOP

NOP

NOP

NOP

DQM

CLK

DQ

D

OUT

n

T2

T1

T4

T3

T0

COMMAND

ADDRESS

BANK,

COL

n

WRITE

D

IN

b

BANK,

COL

b

T5

DS

t

t

HZ

NOTE:

A CAS latency of three is used for illustration. The

READ command

may be to any bank, and the WRITE command may be to any bank.

Figure 10

READ To WRITE With

Extra Clock Cycle

Figure 9

READ To WRITE

Data from any READ burst may be truncated with a

subsequent WRITE command, and data from a fixed-

length READ burst may be immediately followed by

data from a WRITE command (subject to bus turn-

around limitations). The WRITE burst may be initiated

on the clock edge immediately following the last (or last

desired) data element from the READ burst, provided

that I/O contention can be avoided. In a given system

design, there may be a possibility that the device driv-

ing the input data will go Low-Z before the SDRAM DQs

go High-Z. In this case, at least a single-cycle delay

should occur between the last read data and the WRITE

command.

The DQM input is used to avoid I/O contention, as

shown in Figures 9 and 10. The DQM signal must be

asserted (HIGH) at least two clocks prior to the WRITE

command (DQM latency is two clocks for output buff-

ers) to suppress data-out from the READ. Once the

WRITE command is registered, the DQs will go High-Z

(or remain High-Z), regardless of the state of the DQM

signal; provided the DQM was asserted the clock just

prior to the WRITE command which truncated the READ

command. If not, the second WRITE will be an invalid

WRITE. For example, if DQM was low during T4 in fig-

ure 10, then the WRITEs at T5 and T7 would be valid

while the WRITE at T6 would be invalid.

The DQM signal must be de-asserted prior to the

WRITE command (DQM latency is zero clocks for input

buffers) to ensure that the written data is not masked.

Figure 9 shows the case where the clock frequency al-

lows for bus contention to be avoided without adding a

NOP cycle, and Figure 10 shows the case where the

additional NOP is needed.

相关PDF资料 |

PDF描述 |

|---|---|

| MT48LC4M16A2 | SYNCHRONOUS DRAM |

| MT48LC16M4A2 | RSD Series - Econoline Unregulated DC-DC Converters; Input Voltage (Vdc): 24V; Output Voltage (Vdc): 3.3V; Power: 1W; 1kVDC and 3kVDC Isolation Options; Approved for Medical Applications; Suitable for Automated Assembly; 8, 10 and 12 pin Pinning Style Options; Optional Continuous Short Circuit Protected; Efficiency to 85% |

| MT48LC8M16A2 | SYNCHRONOUS DRAM |

| MT48V2M32LFFC | 512K x 32 x 4 banks 2.5V SDRAM(2.5V,512K x 32 x 4组同步动态RAM) |

| MT48V4M32LFFC | SYNCHRONOUS DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT48LC2M3B2B51 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:SDR SDRAM MT48LC2M32B2 a?? 512K x 32 x 4 Banks |

| MT48LC2M8A1 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:SYNCHRONOUS DRAM |

| MT48LC2M8A1TGS | 制造商:MICRON 制造商全称:Micron Technology 功能描述:SYNCHRONOUS DRAM |

| MT48LC2M8A2 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:SYNCHRONOUS DRAM |

| MT48LC32M16A2 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:512Mb x4, x8, x16 SDRAM |

发布紧急采购,3分钟左右您将得到回复。