- 您现在的位置:买卖IC网 > PDF目录69040 > MT8952BPR (ZARLINK SEMICONDUCTOR INC) 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 PDF资料下载

参数资料

| 型号: | MT8952BPR |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| 封装: | PLASTIC, MS-018AB, LCC-28 |

| 文件页数: | 12/32页 |

| 文件大小: | 602K |

| 代理商: | MT8952BPR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

MT8952B

Data Sheet

2

Zarlink Semiconductor Inc.

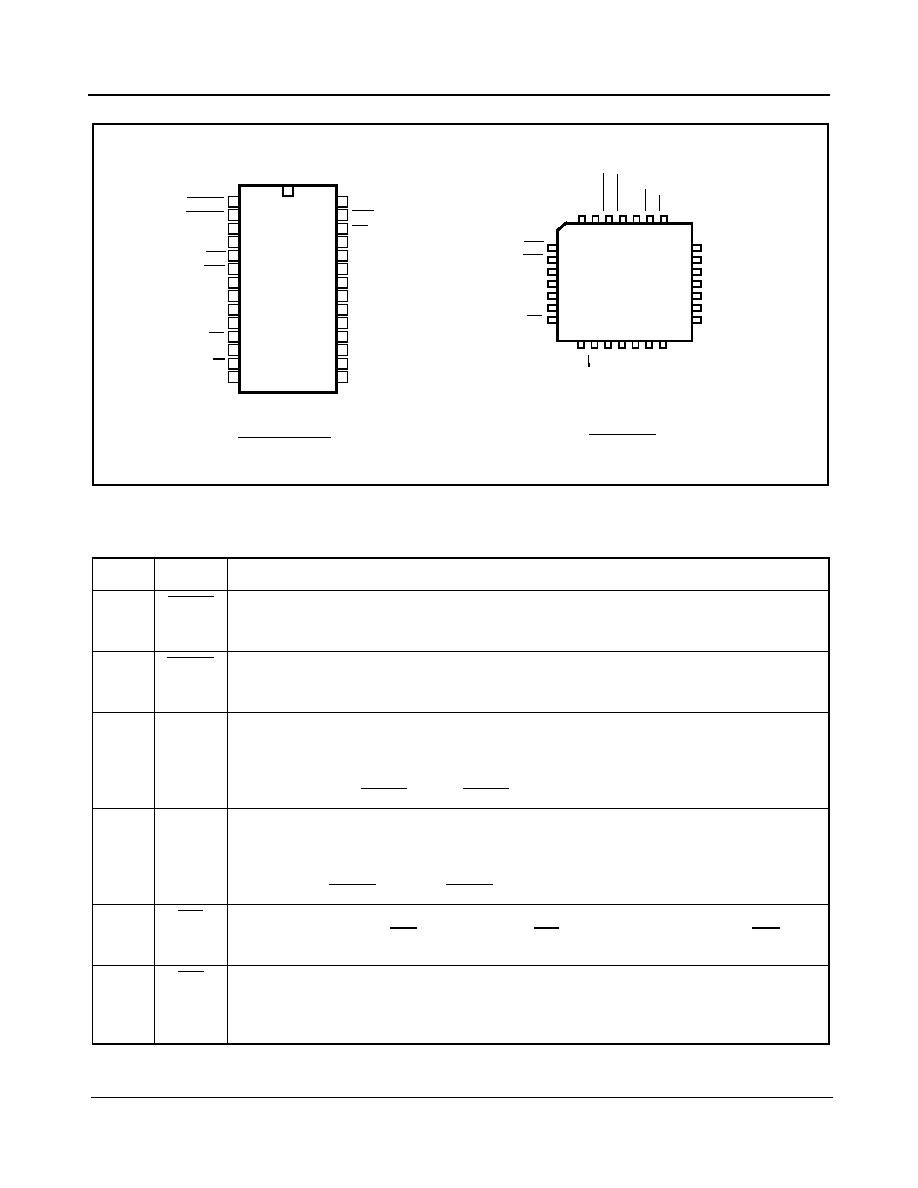

Figure 2 - Pin Connections

Pin Description

Pin No.

Name

Description

1TxCEN

Transmit Clock Enable - This active LOW input enables the transmit section in the External Timing

Mode. When LOW, CDSTo is enabled and when HIGH, CDSTo is in high impedance state. If the

Protocol Controller is in the Internal Timing Mode, this input is ignored.

2RxCEN Receive Clock Enable - This active LOW input enables the receive section in the External Timing

Mode. When LOW, CDSTi is enabled and when HIGH, the clock to the receive section is inhibited. If

the Protocol Controller is in the Internal Timing Mode, this input is ignored.

3CDSTo

C and D channel Output in ST-BUS format - This is the serial formatted data output from the

transmitter in NRZ form. It is in ST-BUS format if the Protocol Controller is in Internal Timing Mode

with the data in selected timeslots (0,2,3 and 4) and the C-channel information in timeslot No. 1. If

the Protocol Controller is in External Timing Mode, the formatted data is output on the rising edge of

the clock (CKi) when TxCEN LOW. If TxCEN is HIGH, CDSTo is in high impedance state.

4CDSTi

C and D channel Input in ST-BUS format - This is the serial formatted data input to the receiver in

NRZ form. It must be in ST-BUS format if the Protocol Controller is in Internal Timing Mode with

the input data in selected timeslots (0,2,3 and 4) and the C-channel information in timeslot No.1. If

the Controller is in External Timing Mode, the serial input data is sampled on the falling edge of the

clock CKi when RxCEN is LOW. If RxCEN is HIGH, the clock to receive section is inhibited.

5WD

Watch-Dog Timer output - Normally a HIGH level output, going LOW if the Watchdog timer times

out or if the external reset (RST) is held LOW. The WD output remains LOW as long as RST is held

LOW.

6IRQ

Interrupt Request Output (Open Drain) - This active LOW output notifies the controlling

microprocessor of an interrupt request. It goes LOW only when the bits in the Interrupt Enable

Register are programmed to acknowledge the source of the interrupt as defined in the Interrupt Flag

Register.

28 PIN PLCC

TxCEN

RxCEN

CDSTo

CDSTi

WD

IRQ

A0

A1

A2

A3

CS

E

R/W

VSS

VDD

RST

F0i

CKi

TEOP

REOP

D7

D6

D5

D4

D3

D2

D1

D0

28 PIN PDIP/SOIC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

28

27

26

25

24

23

22

21

4

5

6

7

8

9

10

11

25

24

23

22

21

20

19

C

D

S

T

i

CKi

TEOP

REOP

D7

D6

D5

D4

WD

IRQ

A0

A1

A2

A3

CS

D

2

3

2

1

28

27

26

12 13

14

15

16

17

18

C

D

S

T

o

R

xC

E

N

T

xC

E

N

V

D

R

S

T

F

0i

E

R

/W

VS

S

D

0

D

1

D

3

相关PDF资料 |

PDF描述 |

|---|---|

| MT8952BP1 | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| MTA41110/P | SPECIALTY MICROPROCESSOR CIRCUIT, PDIP18 |

| MTA41110/SO | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO18 |

| MTR80C186-12 | 16-BIT, 12.5 MHz, MICROPROCESSOR, CQCC68 |

| MTA80C186-10 | 16-BIT, 10 MHz, MICROPROCESSOR, CPGA68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT8952BPR1 | 制造商:Microsemi Corporation 功能描述:PB FREE HDLC CONTROLLER, PLCC - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE HDLC CONTROLLER, PLCC - Tape and Reel |

| MT8952BS | 制造商:Microsemi Corporation 功能描述: |

| MT8952BS1 | 制造商:Microsemi Corporation 功能描述:PB FREE HDLC PROTOCOL CONTROLLER - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE HDLC PROTOCOL CONTROLLER |

| MT8960 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:Integrated PCM Filter Codec |

| MT8960AE | 制造商:ZARLINK 功能描述: |

发布紧急采购,3分钟左右您将得到回复。