- 您现在的位置:买卖IC网 > PDF目录69040 > MT8952BPR (ZARLINK SEMICONDUCTOR INC) 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 PDF资料下载

参数资料

| 型号: | MT8952BPR |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| 封装: | PLASTIC, MS-018AB, LCC-28 |

| 文件页数: | 2/32页 |

| 文件大小: | 602K |

| 代理商: | MT8952BPR |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

MT8952B

Data Sheet

10

Zarlink Semiconductor Inc.

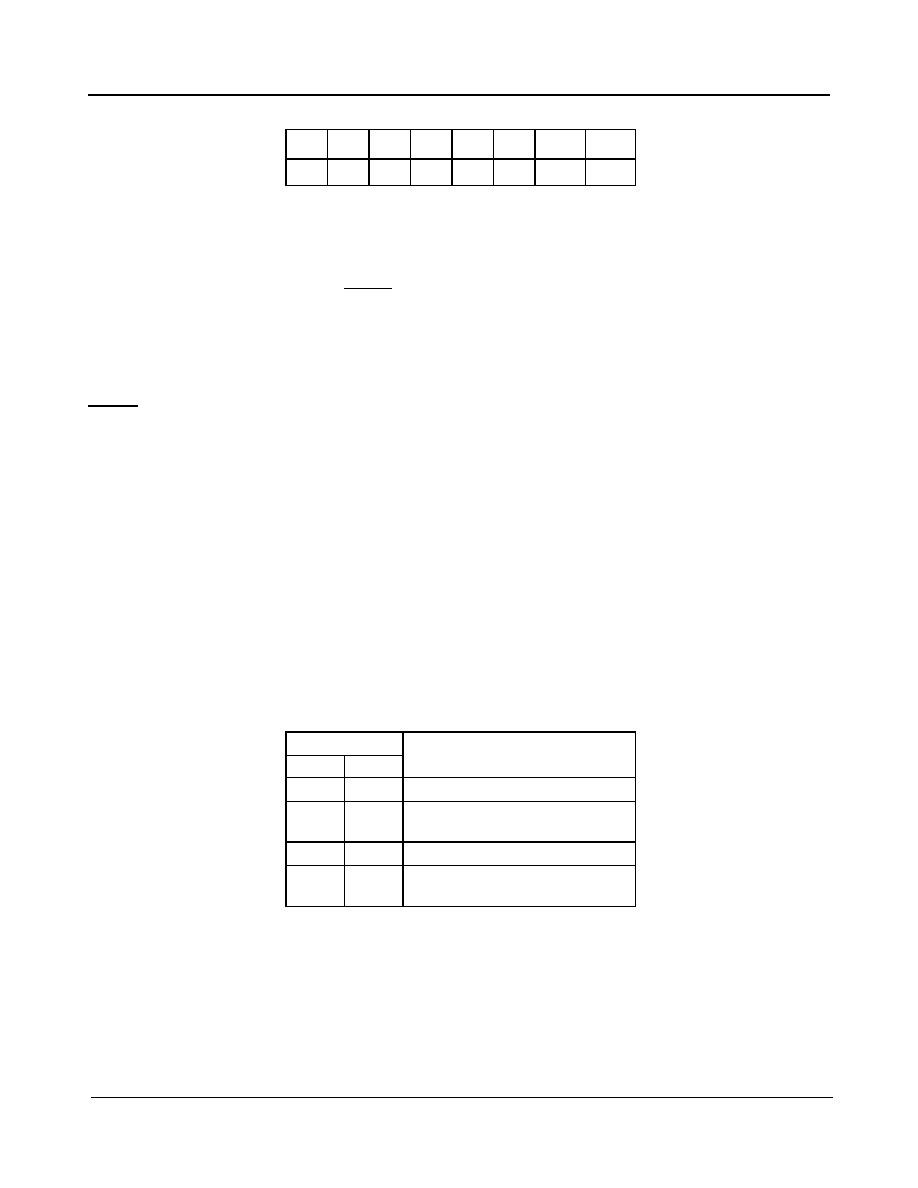

Figure 7 - Control Register

TxEN -Transmit Enable: When set HIGH, this bit enables the transmitter and when LOW, disables it setting the

serial output (CDSTo) to high impedance state. If the transmitter is disabled during the transmission of a packet

using this bit, the Protocol Controller will wait until the completion of the packet and closing flag is transmitted or the

packet is aborted before setting the output (CDSTo) to high impedance state.

Thus TxEN

bit controls the

transmission packet by packet unlike TxCEN input (pin 1) which controls it bit-by-bit. However, if the Protocol

Controller is in transparent data transfer state, the transmission will be stopped within two bit periods (maximum)

and set the output to high impedance state.

RxEN - Receive Enable: This bit enables the receiver when set HIGH and disables it when LOW. If this bit goes

LOW during the reception of the packet, the receiver can only be disabled after the current packet and its closing

flag are received or an abort is detected. Thus RxEN bit controls the receiver section packet by packet unlike

RxCEN input (pin 2) which controls it bit-by-bit. However, if the Protocol Controller is in transparent data transfer

state, the receiver will be disabled immediately.

RxAD - Receive Address Detect: This bit when set HIGH, enables the address detection for the received packets.

This causes the receiver to recognize only those packets having a unique address as programmed in the Receive

Address Register or if the address byte is the All-Call address (all ONEs). The address comparison is done only on

seven bits (compatible to the first byte of the address field defined in LAPD-CCITT) and an All-Call is defined as all

ONEs in upper seven bits of the received address field. If RxAD is LOW, the address detection is disabled and

every valid packet is recognized.

RA6/7 - Receive Address Six/Seven bits: This bit, when set HIGH, limits the address detection only to the upper

six bits of the received address byte (last 6 bits of received address field) and when LOW, allows the address

comparison on seven bits. An "all call", in this case is defined as all ONEs in the upper six bits only. RA6/7 is

ignored if the address detection is disabled (RxAD=0).

IFTF0 and IFTF1 - Interframe Time Fill: Setting these bits according to the table below (Table 6) causes the

transmitter to be in one of the active or idle states or allows the Protocol Controller to be in the transparent data

transfer state.

Table 6 - Interframe Time Fill Bits

FA - Frame Abort: When set HIGH, this bit’tags’ the next byte written to the transmit FIFO and causes an abort

sequence (eight ONEs) to be transmitted when it reaches the bottom of the FIFO. The abort sequence will be

transmitted instead of the byte that was tagged. The FA bit is cleared to ZERO upon writing the data to the transmit

FIFO. As a result, a ‘read’ of this register bit will not reflect the last data written to it.

EOP - End Of Packet: Writing a ONE to this bit ‘tags’ the next byte written to the transmit FIFO to indicate that it is

the last data byte of the packet. This bit is cleared to ZERO upon writing the data to the transmit FIFO. As a result,

a read of this register bit will not indicate the last data written to it.

D7

D6

D5

D4

D3

D2

D1

D0

TxEN RxEN RxAD RA6/7 IFTF1 IFTF0

FA

EOP

IFTF Bits

Result

IFTF1

IFTF0

0

Idle State (All ONEs)

0

1

Interframe Time Fill state

(Continuous Flags)

1

0

Transparent Data Transfer

1

Go Ahead state (Continuous

7FHEX)

相关PDF资料 |

PDF描述 |

|---|---|

| MT8952BP1 | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| MTA41110/P | SPECIALTY MICROPROCESSOR CIRCUIT, PDIP18 |

| MTA41110/SO | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO18 |

| MTR80C186-12 | 16-BIT, 12.5 MHz, MICROPROCESSOR, CQCC68 |

| MTA80C186-10 | 16-BIT, 10 MHz, MICROPROCESSOR, CPGA68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT8952BPR1 | 制造商:Microsemi Corporation 功能描述:PB FREE HDLC CONTROLLER, PLCC - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE HDLC CONTROLLER, PLCC - Tape and Reel |

| MT8952BS | 制造商:Microsemi Corporation 功能描述: |

| MT8952BS1 | 制造商:Microsemi Corporation 功能描述:PB FREE HDLC PROTOCOL CONTROLLER - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE HDLC PROTOCOL CONTROLLER |

| MT8960 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:Integrated PCM Filter Codec |

| MT8960AE | 制造商:ZARLINK 功能描述: |

发布紧急采购,3分钟左右您将得到回复。