- 您现在的位置:买卖IC网 > PDF目录69040 > MT8952BPR (ZARLINK SEMICONDUCTOR INC) 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 PDF资料下载

参数资料

| 型号: | MT8952BPR |

| 厂商: | ZARLINK SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| 封装: | PLASTIC, MS-018AB, LCC-28 |

| 文件页数: | 30/32页 |

| 文件大小: | 602K |

| 代理商: | MT8952BPR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页

MT8952B

Data Sheet

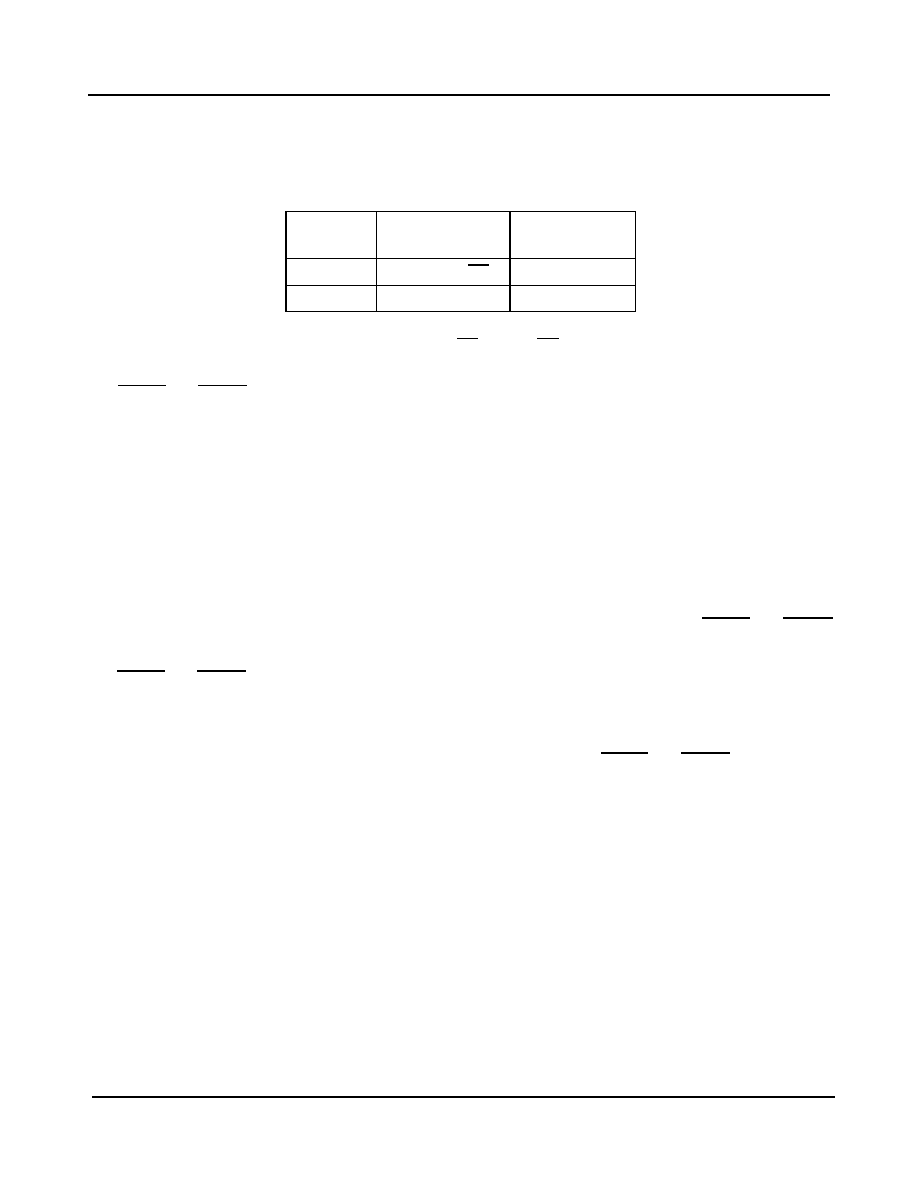

7

Zarlink Semiconductor Inc.

reserves one channel (channel-1) on the ST-BUS for carrying control information (C-channel) and this timeslot can

not be used for the packetized data. While the Protocol Controller is in the Internal Timing Mode, the clock input CKi

can be either at the bit rate or at 2×bit rate depending on the BRCK bit in the Timing Control Register as shown in

Table 2.

Table 2 - Output Bit Rate In Internal Timing Mode

The Protocol Controller uses the ST-BUS timing signals F0i and C2i/C4i, and enables the transmitter and receiver

sections in the appropriate timeslots as determined by TC0-TC3 bits in the Timing Control Register.

The TxCEN and RxCEN inputs are ignored in this mode.

C-Channel Interface

This is a separate control channel (C-channel) interface relevant only in the Internal Timing Mode. The data stored

in the C-Channel Control Register is shifted out during the channel-1 timeslot of the outgoing ST-BUS (CDSTo) and

the C1EN bit in the Timing Control Register enables the transmission. The transmission of C-Channel is

independent of packet/data transmission. The data received on channel-1 of the incoming ST-BUS (CDSTi) is

shifted into the C-Channel Status Register independently and it is updated continuously.

Both the C-channel registers are accessible by the accompanying CPU through the parallel port.

External Timing Mode

In the External Timing Mode, the transmit and receive sections are enabled independently by TxCEN and RxCEN

control inputs and the formatted data packets are shifted in/out serially at a rate equal to the clock frequency on

CKi. The output is transmitted on the rising edge and the receiver samples the input on the falling edge of the clock.

The TxCEN and RxCEN controls are independent and asynchronous and have effect only after the current bit in the

packet is transmitted/received.

Although the protocol controller provides the packetized data on a limited number of channels on the ST-BUS while

operating in the Internal Timing Mode, it can packetize the data on any or all the channels of the ST-BUS if it is

operated in the External Timing Mode with appropriate

enable signals on TxCEN and RxCEN.

Transparent Data Transfer

By setting the IFTF bits in the Control Register appropriately, the protocol functions can be disabled. This provides

a bidirectional access to the serial port through the microprocessor interface, with 19 byte deep FIFO in each

direction. The transparent data transfer facility functions in bytewide format and is available in both timing modes

except when the timing control bits are set for one bit/frame during the Internal Timing Mode.

The transmit data is shifted out serially on CDSTo and the operation being bytewide, only the least significant bits of

each byte loaded are transmitted, if the timing control bits are set to select 2, 6 or 7 bits/frame. When the transmit

FIFO is empty, the last byte or the portion the last byte, written to the FIFO is transmitted repeatedly. Similarly the

serial data on CDSTi is shifted in and converted to bytewide format. In case the timeslot selected is 2, 6 or 7

bits/frame, the reception involves only the most significant bits of each byte.

It should be noted that none of the protocol related status or interrupt bits are applicable in transparent data transfer

state. However, the FIFO related status and interrupt bits are pertinent and carry the same meaning as they do

while performing the protocol functions.

BRCK Bit

CKi Input

Output Data

Rate

0

4.096 MHz/C4i

2.048 Mbps

1

2.048 MHz/C2i

2.048 Mbps

相关PDF资料 |

PDF描述 |

|---|---|

| MT8952BP1 | 1 CHANNEL(S), 2.5M bps, SERIAL COMM CONTROLLER, PQCC28 |

| MTA41110/P | SPECIALTY MICROPROCESSOR CIRCUIT, PDIP18 |

| MTA41110/SO | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO18 |

| MTR80C186-12 | 16-BIT, 12.5 MHz, MICROPROCESSOR, CQCC68 |

| MTA80C186-10 | 16-BIT, 10 MHz, MICROPROCESSOR, CPGA68 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT8952BPR1 | 制造商:Microsemi Corporation 功能描述:PB FREE HDLC CONTROLLER, PLCC - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE HDLC CONTROLLER, PLCC - Tape and Reel |

| MT8952BS | 制造商:Microsemi Corporation 功能描述: |

| MT8952BS1 | 制造商:Microsemi Corporation 功能描述:PB FREE HDLC PROTOCOL CONTROLLER - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE HDLC PROTOCOL CONTROLLER |

| MT8960 | 制造商:ZARLINK 制造商全称:Zarlink Semiconductor Inc 功能描述:Integrated PCM Filter Codec |

| MT8960AE | 制造商:ZARLINK 功能描述: |

发布紧急采购,3分钟左右您将得到回复。