- 您现在的位置:买卖IC网 > PDF目录98143 > ST52510F3M6 (STMICROELECTRONICS) MICROCONTROLLER, PDSO20 PDF资料下载

参数资料

| 型号: | ST52510F3M6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | MICROCONTROLLER, PDSO20 |

| 封装: | SOP-20 |

| 文件页数: | 53/136页 |

| 文件大小: | 3335K |

| 代理商: | ST52510F3M6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页当前第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页

Obsolete

Product(s)

- Obsolete

Product(s)

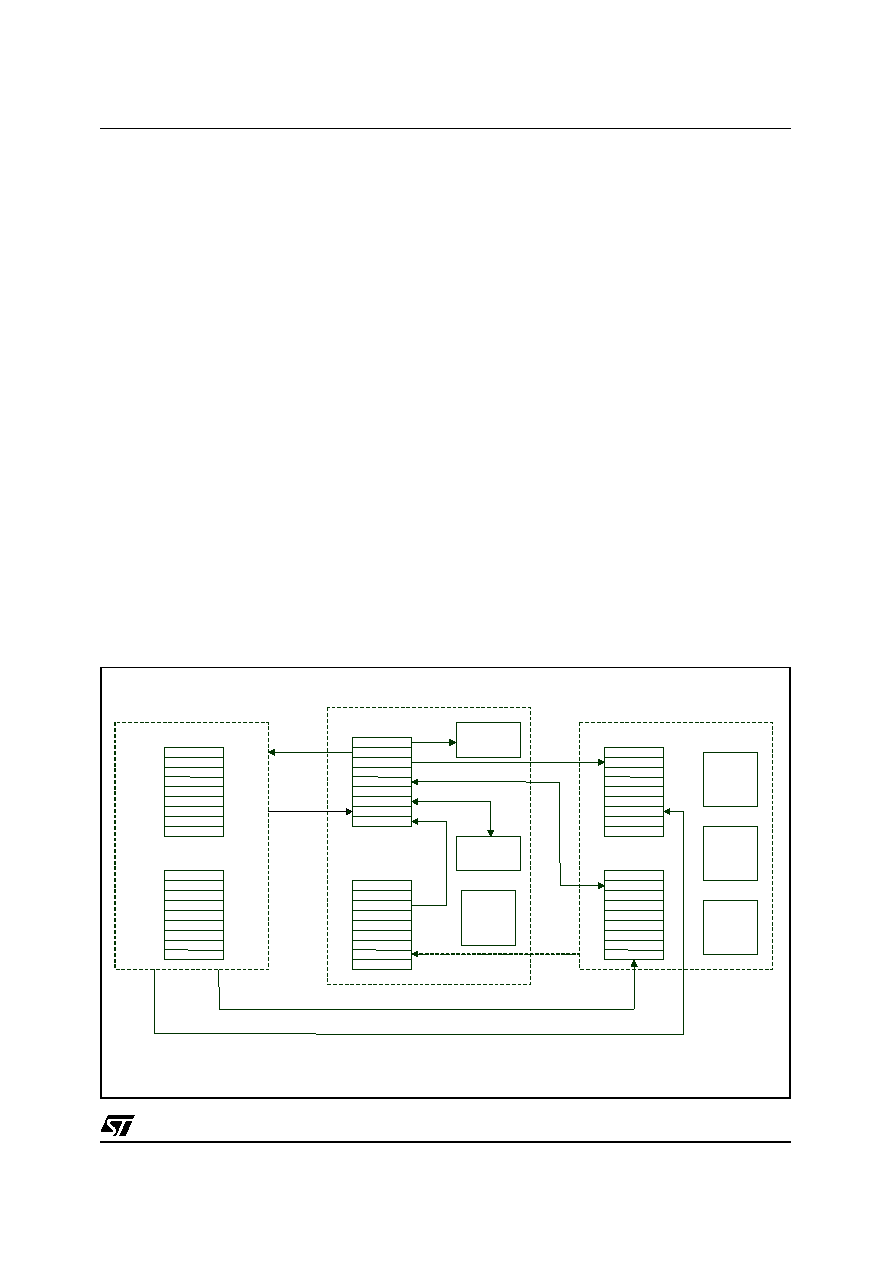

3 ADDRESSING SPACES

ST52F510/F513 has six separate addressing

spaces:

■ Register File

■ Program/Data Memory and Stacks

■ Input Registers

■ Output Registers

■ Configuration Registers

■ Fuzzy Registers

Note: stack is in the same address space of

Program memory.

Each space is addressed by a load type instruction

that indicates the source and the destination space

in the mnemonic code (see Figure 3.1).

3.1 Memory Interface

The read/write operation in the space addresses

are managed by the Memory Interface, which can

recognize the type of memory addressed and set

the appropriate access time and mode.

In addition, the Memory Interface manages the In

Application Programming (IAP) functions in Flash

devices like writing cycle and memory write

protection.

Figure 3.1 Addressing Spaces

3.2 Register File

The Register File consists of 256 general purpose

8-bit RAM locations called “registers” in order to

recall the functionality.

The Register File exchanges data with all the other

addressing spaces and is used by the ALU to

perform all the arithmetic and logic instructions.

These instructions have any Register File address

as operands.

Data can be moved from one location to another by

using the LDRR instruction; see further ahead for

information on the instruction used to move data

between the Register File and the other

addressing spaces.

3.3 Program/Data Memory

The Program/Data Memory consists of both non-

volatile memory (Flash, EEPROM) and RAM

memory benches.

Non-volatile memory (NVM) is mainly used to store

the user program and can also be used to store

permanent data (constant, look-up tables).

Each RAM bench consists of 256 locations used to

store run-time user data. At least one bench is

present in the devices. RAM benches are also

used to implement both System and User Stacks.

NVM & RAM locations can be accessed by means

of the LDER and LDRE instructions.

CU

DPU

ALU

PERIPHERAL

BLOCK

REGISTER FILE

INPUT REGISTERS

NON VOLATILE MEMORY

RAM BANKS

AND STACKS

PROGRAM/DATA MEMORY

STFive CORE

ON CHIP PERIPHERALS

OUTPUT

REGISTERS

CONFIGURATION

REGISTERS

PERIPHERAL

BLOCK

PERIPHERAL

BLOCK

LDER

LDRE

LDRI

LDCE

LDCR

DECISION

PROCESSOR

REGISTERS

LDFR

LDPE

LDPR

LDCNF

PROGRAM

COUNTER

PGSETR

GETPG

相关PDF资料 |

PDF描述 |

|---|---|

| ST52E430B/D | 8-BIT, UVPROM, 20 MHz, MICROCONTROLLER, CDIP32 |

| ST52F510F1M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO20 |

| ST52F510G0B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 |

| ST52F513F0M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO20 |

| ST52F513F1B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST52510G2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT ICU WITH 10-BIT ADC. TWO TIMERS/PWM. I2C. SPI. SCI. UP TO 8K FLASH |

| ST52510G3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT ICU WITH 10-BIT ADC. TWO TIMERS/PWM. I2C. SPI. SCI. UP TO 8K FLASH |

| ST52510K2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT ICU WITH 10-BIT ADC. TWO TIMERS/PWM. I2C. SPI. SCI. UP TO 8K FLASH |

| ST52510K3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT ICU WITH 10-BIT ADC. TWO TIMERS/PWM. I2C. SPI. SCI. UP TO 8K FLASH |

| ST52510Y2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-BIT ICU WITH 10-BIT ADC. TWO TIMERS/PWM. I2C. SPI. SCI. UP TO 8K FLASH |

发布紧急采购,3分钟左右您将得到回复。