- 您现在的位置:买卖IC网 > PDF目录271212 > ST72F324BK6TATRE (STMICROELECTRONICS) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP32 PDF资料下载

参数资料

| 型号: | ST72F324BK6TATRE |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP32 |

| 封装: | 7 X 7 MM, ROHS COMPLIANT, LQFP-32 |

| 文件页数: | 118/197页 |

| 文件大小: | 3593K |

| 代理商: | ST72F324BK6TATRE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页当前第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页

Obsolete

Product(s)

- Obsolete

Product(s)

ST72324B-Auto

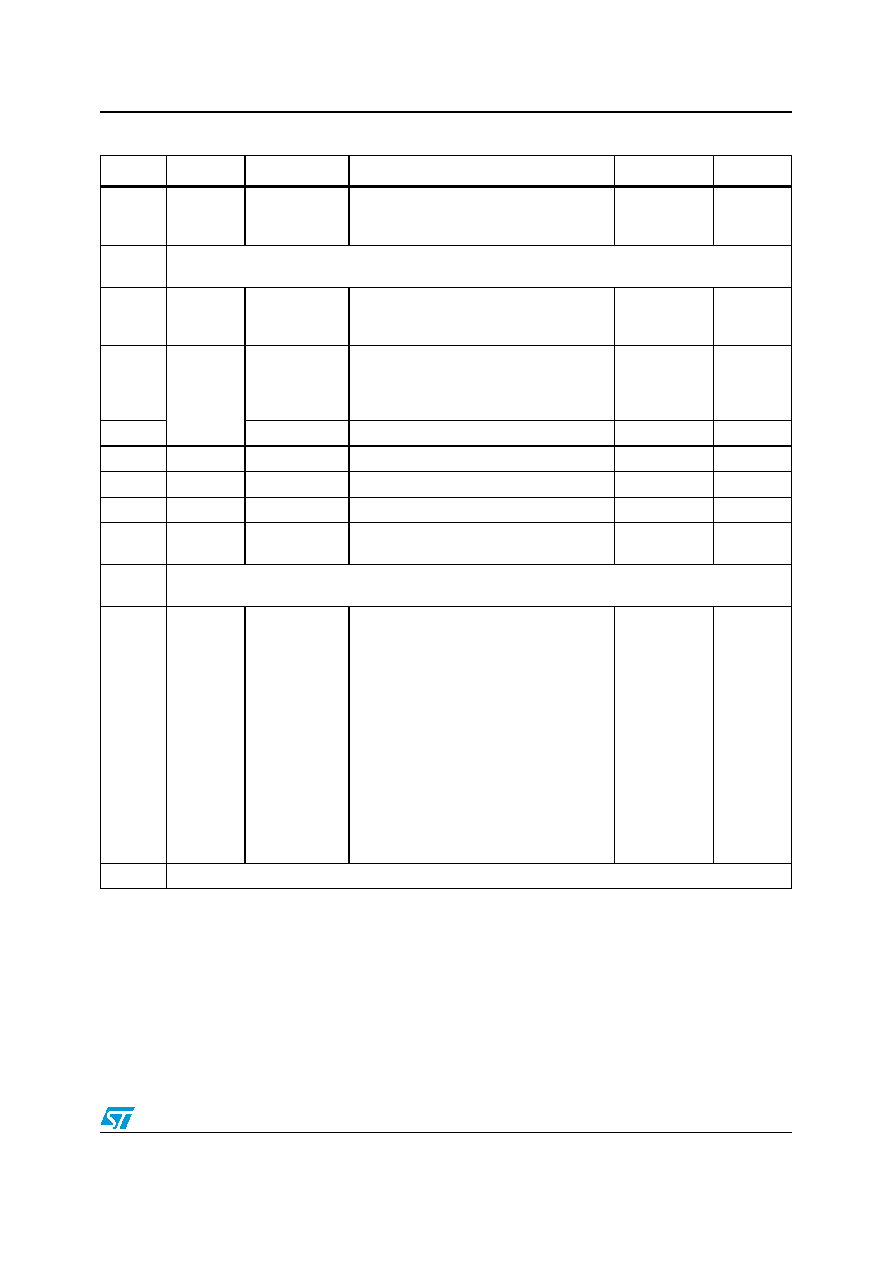

Register and memory map

27/197

000Fh

0010h

0011h

Port F(1)

PFDR

PFDDR

PFOR

Port F data register

Port F data direction register

Port F option register

00h

R/W

0012h to

0020h

Reserved area (15 bytes)

0021h

0022h

0023h

SPI

SPIDR

SPICR

SPICSR

SPI data I/O register

SPI control register

SPI control/status register

xxh

0xh

00h

R/W

0024h

0025h

0026h

0027h

ITC

ISPR0

ISPR1

ISPR2

ISPR3

Interrupt software priority register 0

Interrupt software priority register 1

Interrupt software priority register 2

Interrupt software priority register 3

FFh

R/W

0028h

EICR

External interrupt control register

00h

R/W

0029h

Flash

FCSR

Flash control/status register

00h

R/W

002Ah

Watchdog

WDGCR

Watchdog control register

7Fh

R/W

002Bh

SI

SICSR

System integrity control/status register

000x 000xb

R/W

002Ch

002Dh

MCC

MCCSR

MCCBCR

Main clock control/status register

Main clock controller: beep control register

00h

R/W

002Eh to

0030h

Reserved area (3 bytes)

0031h

0032h

0033h

0034h

0035h

0036h

0037h

0038h

0039h

003Ah

003Bh

003Ch

003Dh

003Eh

003Fh

Timer A

TACR2

TACR1

TACSR

TAIC1HR

TAIC1LR

TAOC1HR

TAOC1LR

TACHR

TACLR

TAACHR

TAACLR

TAIC2HR

TAIC2LR

TAOC2HR

TAOC2LR

Timer A control register 2

Timer A control register 1

Timer A control/status register

Timer A input capture 1 high register

Timer A input capture 1 low register

Timer A output compare 1 high register

Timer A output compare 1 low register

Timer A counter high register

Timer A counter low register

Timer A alternate counter high register

Timer A alternate counter low register

Timer A input capture 2 high register

Timer A input capture 2 low register

Timer A output compare 2 high register

Timer A output compare 2 low register

00h

xxxx x0xxb

xxh

80h

00h

FFh

FCh

FFh

FCh

xxh

80h

00h

R/W

Read only

R/W

Read only

R/W

0040h

Reserved area (1 byte)

Table 3.

Hardware register map (continued)

Address

Block

Register label

Register name

Reset status

Remarks

相关PDF资料 |

PDF描述 |

|---|---|

| SAB-C161K-LMHA | 16-BIT, 20 MHz, MICROCONTROLLER, PQFP80 |

| ST72P561R4TA/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| ST7263BH4T1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP48 |

| S912XDT384J1VAGR | 16-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP144 |

| SC101161DGCFUR2 | 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72F324BK6TAXS | 制造商:STMicroelectronics 功能描述: |

| ST72F324BK6TCE | 制造商:STMicroelectronics 功能描述: |

| ST72F324BK6TCS | 制造商:STMicroelectronics 功能描述:APG |

| ST72F324BK6TCTRE | 制造商:STMicroelectronics 功能描述:LQFP 32 7x7x1.4 1 |

| ST72F324J2B6 | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。